- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361297 > QL901M-6PS680C (Electronic Theatre Controls, Inc.) Electrical Spring Connector; Contact Termination:Twist On; Wire Size (AWG):14-10; Body Material:Flame retardant nylon; Contact Material:Spring Steel; Pack Quantity:100; Series:512; Size:2-#18 up to 5-#12; Voltage Rating:600V RoHS Compliant: Yes PDF資料下載

參數(shù)資料

| 型號(hào): | QL901M-6PS680C |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Electrical Spring Connector; Contact Termination:Twist On; Wire Size (AWG):14-10; Body Material:Flame retardant nylon; Contact Material:Spring Steel; Pack Quantity:100; Series:512; Size:2-#18 up to 5-#12; Voltage Rating:600V RoHS Compliant: Yes |

| 中文描述: | QuickMIPS ESP家庭 |

| 文件頁數(shù): | 1/37頁 |

| 文件大小: | 432K |

| 代理商: | QL901M-6PS680C |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

QL901M QuickMIPS

TM

Data Sheet Rev B

1

QL901M QuickMIPS Data Sheet

QuickMIPS ESP Family

1.0 Overview

The QuickMIPS Embedded Standard Products

(ESPs) family provides an out-of-the box solution

consisting of the QL901M QuickMIPS chip and

the QuickMIPS development environment. The

development environment includes a Reference

Design Kit (RDK) with drivers, real-time

operating systems, and QuickMIPS system

model. With the RDK, software and hardware

engineers can evaluate, debug, and emulate

their system in parallel.

CPU

High-performance MIPS 4Kc processor runs

up to 133 MHz in .25

μ

(173 Dhrystone MIPS)

1.3 Dhrystone MIPS per MHz

MDU supports MAC instructions for

DSP functions

16 Kbytes of Instruction Cache

(4-way set associative)

16 Kbytes of Data Cache (4-way set

associative) with lockout capability per line

High-Performance Bus (AMBA AHB)

High-performance 32-bit AMBA AHB bus

standard for high-speed system bus running

at half the CPU clock

High-bandwidth memory controller for

SDRAM, SRAM, and EPROM

SDRAM support for standard SDRAMs up to

256 MBytes with auto refresh, up to 4 banks

non-interleaved

Support for PC100 type memories with up

to two chip enables

EPROM controller for boot code

8-bit, 16-bit, and 32-bit device width support

16 Kbytes of on-chip, high-speed SRAM for

use by multiple AHB Bus Masters

32-bit 66/33 MHz PCI Host and Satellite

(Master/Target) operation with DMA

channels and FIFO for full bandwidth

Two MAC10/100s with MII ports connect

easily to external transceivers/PHY devices

One AHB 32-bit master port/one AHB

32-bit slave port to Programmable Fabric

Global System Configuration and Interrupt

Controller

Peripheral Bus (AMBA APB)

32-bit APB runs at half the CPU clock

frequency (the same as the AHB clock)

Three APB slave ports in the programmable

fabric

Two serial ports (one with Modem control

signals and one with IRDA-compliant signals)

Four general-purpose 32-bit timer/counters

on one APB port

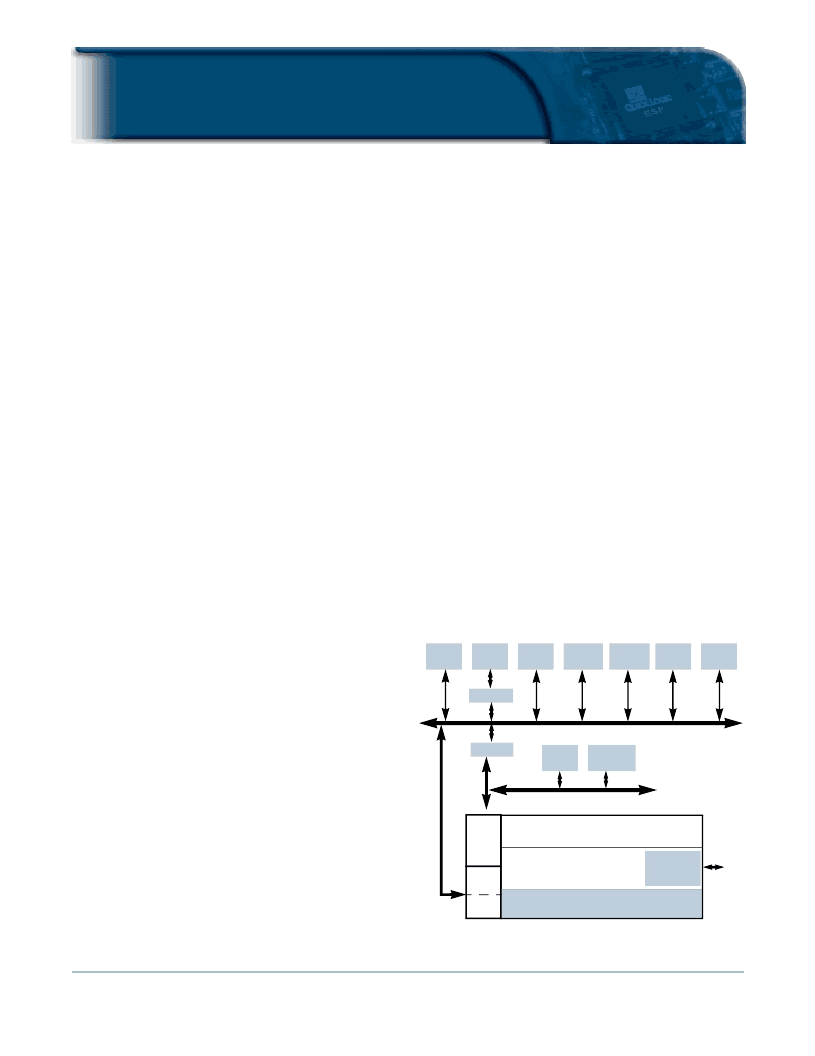

Figure 1: Embedded QuickMIPS Block Diagram

ECI to AHB

AHB to APB

16 Kbytes

SRAM

MIPS 4Kc

w/Caches

32-bit PCI

66/33 MHz

Ethernet

10/100 MAC

Ethernet

10/100 MAC

Memory

Controller

Interrupt

Controller

Two 16550

UARTs

Four 32-bit

Timer/Counters

32-bit Advanced Peripheral Bus

36 RAM Blocks (Configurations 128x18; 256x9; 512x4; or 1024x2)

3 APB

Slave

I/F

1 AHB

1 AHB

Slave I/F

Via-Link Programmable Fabric

Configurable

Logic Analyzer

Monitor (CLAM)

JTAG

18 ECU Blocks-- 8x8 Multiply, 16-bit carry/add

32-bit Advanced High-Performance Bus

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QL901M-6PS680I | QuickMIPS ESP Family |

| QLA694B-2G | PCB MOUNT LED INDICATORS |

| QLA694B-2H | PCB MOUNT LED INDICATORS |

| QLA694B-2I | PCB MOUNT LED INDICATORS |

| QLA694B-2Y | PCB MOUNT LED INDICATORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QL901M-6PS680I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:QuickMIPS ESP Family |

| QL902M200-2PS544C-5654M | 制造商:QuickLogic Corporation 功能描述: |

| QL902M200-2PS544C-5994 | 制造商:QuickLogic Corporation 功能描述: |

| QL90F7S-A | 制造商:ROITHNER 制造商全稱:ROITHNER 功能描述:LASER DIODE SPECIFICATIONS FOR APPROVAL |

| QL90F7S-B | 制造商:ROITHNER 制造商全稱:ROITHNER 功能描述:LASER DIODE SPECIFICATIONS FOR APPROVAL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。