- 您現在的位置:買賣IC網 > PDF目錄361316 > QS5919T160Q (INTEGRATED DEVICE TECHNOLOGY INC) LOW SKEW TTL PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER PDF資料下載

參數資料

| 型號: | QS5919T160Q |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | LOW SKEW TTL PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| 中文描述: | PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | QSOP-28 |

| 文件頁數: | 1/9頁 |

| 文件大?。?/td> | 129K |

| 代理商: | QS5919T160Q |

1

INDUSTRIAL TEMPERATURE RANGE

QS5919T

LOW SKEW TTL PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

R

D

Q

Q

0

R

D

Q

Q

1

R

D

Q

Q

2

R

D

Q

Q

3

R

D

Q

Q

4

R

D

Q

Q

5

R

D

Q

Q/2

Q

OE/RST

0

1

1

0

/2

VCO

LOOP

FILTER

PHASE

DETECTOR

1

0

FREQ_SEL

REF_SEL

LOCK

FEEDBACK

SYNC

0

SYNC

1

PLL_EN

2xQ

PE

SEPTEMBER 2000

2000 Integrated Device Technology, Inc.

DSC-5815/-

c

QS5919T

INDUSTRIAL TEMPERATURE RANGE

LOW SKEW TTL PLL

CLOCK DRIVER WITH

INTEGRATED LOOP FILTER

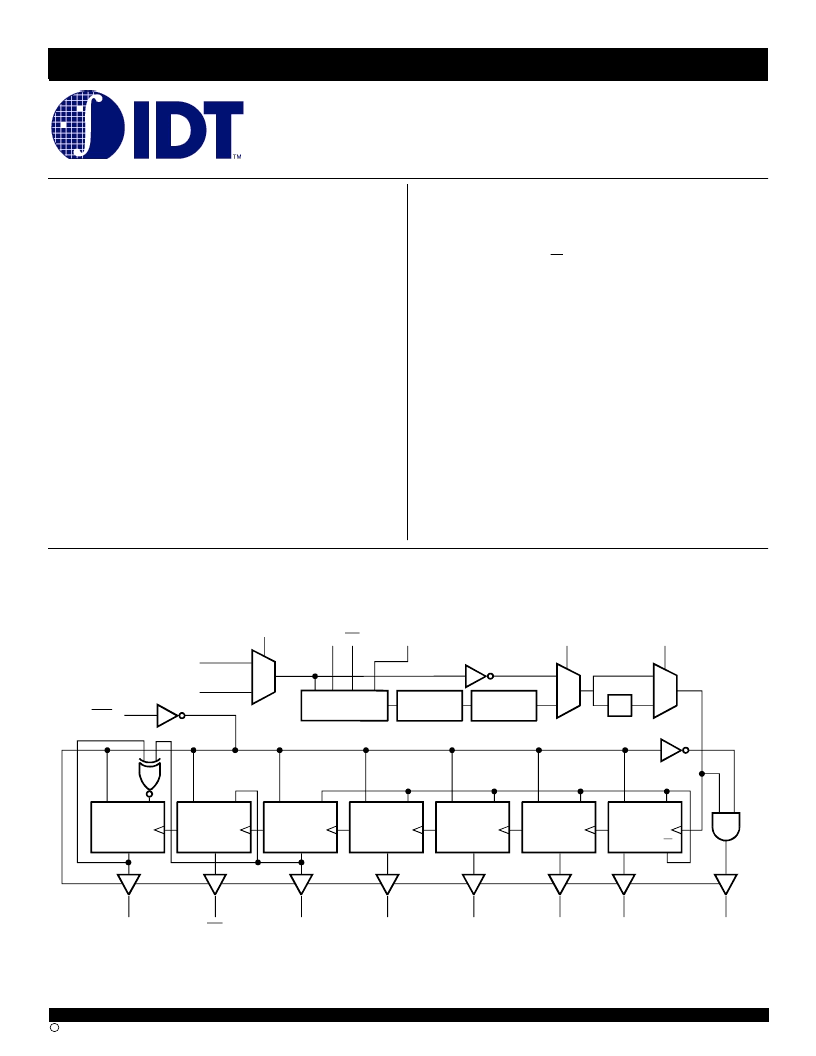

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION

The QS5919T Clock Driver uses an internal phase locked loop (PLL)

to lock low skew outputs to one of two reference clock inputs. Eight outputs

are available: 2xQ, Q

0

-Q

4

, Q

5

, Q/2. Careful layout and design ensure <

350ps skew between the Q

0

-Q

4

, and Q/2 outputs. The QS5919T includes

an internal RC filter which provides excellent jitter characteristics and

elimnates the need for external components. Various combinations of

feedback and a divide-by-2 in the VCO path allow applications to be

customzed for linear VCO operation over a wide range of input SYNC

frequencies. The PLL can also be disabled by the PLL_EN signal to allow

low frequency or DC testing. The LOCK output asserts to indicate when

phase lock has been achieved. The QS5919T is designed for use in high-

performance workstations, multi-board computers, networking hardware,

and mainframe systems. Several can be used in parallel or scattered

throughout a systemfor guaranteed low skew, system-wide clock distribu-

tion networks.

For more information on PLL clock driver products, see Application Note

AN-227.

FEATURES:

5V operation

Low noise TTL level outputs

< 350ps output skew, Q

0

–Q

4

2xQ output, Q outputs,

Q

output, Q/2 output

Outputs 3-state and reset while OE/

RST

low

PLL disable feature for low frequency testing

Internal loop filter RC network

Functional equivalent to Motorola MC88915

Positive or negative edge synchronization (

PE

)

Balanced drive outputs ±24mA

160MHz maximumfrequency (2xQ output)

Available in QSOP and PLCC packages

相關PDF資料 |

PDF描述 |

|---|---|

| QS5919T55J | LOW SKEW TTL PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5919T55Q | LOW SKEW TTL PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5920PA | Ten Distributed-Output Clock Driver |

| QS5920Q | Ten Distributed-Output Clock Driver |

| QS5930 | LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| QS5919T-160TJ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Eight Distributed-Output Clock Driver |

| QS5919T-160TQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Eight Distributed-Output Clock Driver |

| QS5919T55J | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:LOW SKEW TTL PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5919T55Q | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:LOW SKEW TTL PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5919T-55TJ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Eight Distributed-Output Clock Driver |

發(fā)布緊急采購,3分鐘左右您將得到回復。