- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361317 > QS5LV919100Q (INTEGRATED DEVICE TECHNOLOGY INC) 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER PDF資料下載

參數(shù)資料

| 型號: | QS5LV919100Q |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| 中文描述: | 5LV SERIES, PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | QSOP-28 |

| 文件頁數(shù): | 5/12頁 |

| 文件大小: | 98K |

| 代理商: | QS5LV919100Q |

5

INDUSTRIAL TEMPERATURE RANGE

QS5LV919

3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

NOTES:

1. See Test Loads and Waveforms for test load and termnation.

2. Skew specifications apply under identical environments (loading, temperature, V

DD

, device speed grade).

3. Measured in open loop mode PLL_EN = 0.

4. Jitter is characterized with Q output at 20MHz. See Frequency Selection Table for information on proper FREQ_SEL level for specified input frequencies.

5. Skew measured at selected synchronization edge.

6. t

PD

measured at device inputs at 0.5V

DD

, Q output at 80MHz.

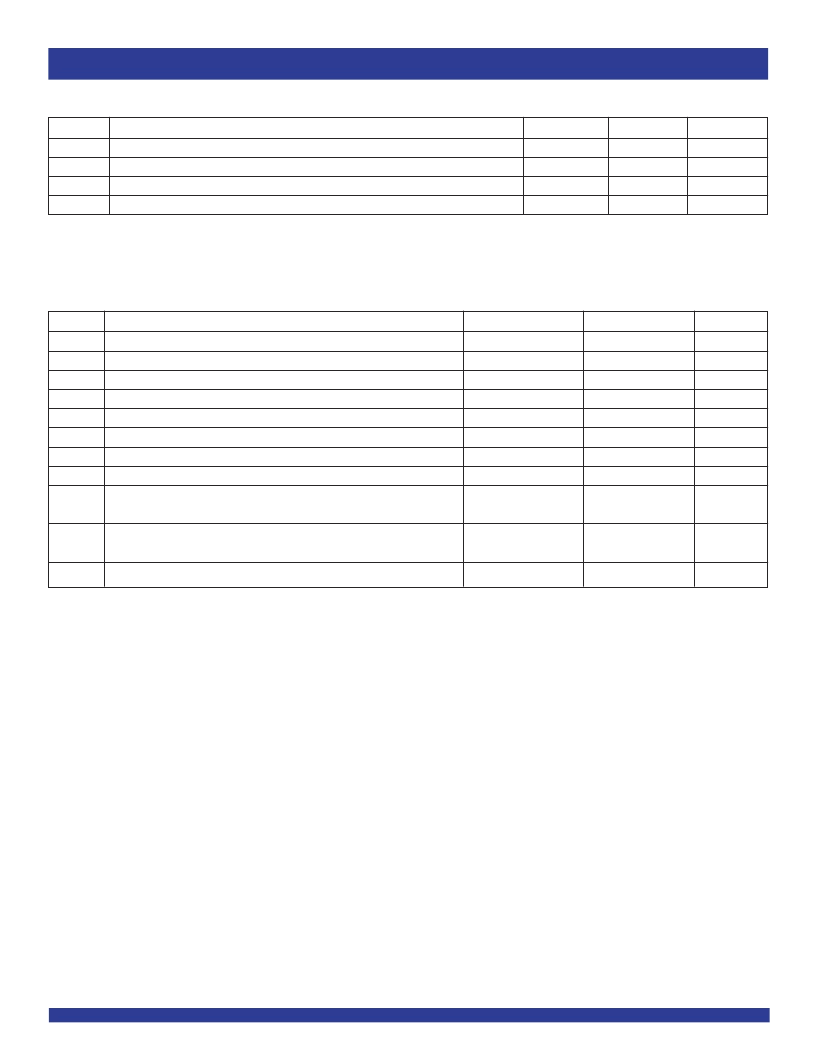

INPUT TIMING REQUIREMENTS

Symbol

Description

(1)

t

R

, t

F

Maximuminput rise and fall times, 0.8V to 2V

F

I

Input Clock Frequency, SYNC

0

, SYNC

1

(1)

t

PWC

Input clock pulse, HIGH or LOW

(2)

D

H

Input duty cycle, SYNC

0

, SYNC

1

(2)

NOTES:

1.

See Output Frequency and Frequency Selection tables for more detail on allowable SYNC input frequencies for different speed grades with different FEEDBACK and

FREQ_SEL combinations.

2.

Where pulse witdh implied by D

H

is less than t

WPC

limt, t

WPC

limt applies

Min.

—

2.5

2

25

Max.

3

100

—

75

Unit

ns

MHz

ns

%

SWITCHING CHARACTERISTICS OV ER OPERATING RANGE

Symbol

t

SKR

t

SKF

t

SKALL

t

PW

t

PW

t

J

t

PD

t

LOCK

t

PZH

t

PZL

t

PHZ

t

PLZ

t

R,

t

F

Parameter

(1)

Output Skew Between Rising Edges, Q

0

-Q

4

(and Q/

2

if

PE

= LOW)

(2)

Output Skew Between Falling Edges, Q

0

-Q

4

(and Q/

2

if

PE

= HIGH)

(2)

Output Skew, All Outputs

(2, 5)

Pulse Width, 2xQ output, >40MHz

Pulse Width, Q

0

-Q

4

, Q

5,

Q/2 outputs, 80MHz

Cycle-to-Cycle Jitter

(4)

SYNC Input to Feedback Delay

(6)

SYNC to Phase Lock

Output Enable Time, OE/

RST

LOW to HIGH

(3)

Min.

—

—

—

Max.

300

300

500

Unit

ps

ps

ps

ns

ns

ns

ps

ms

ns

T

CY

/2

0.4

T

CY

/2

0.4

0.15

500

—

0

T

CY

/2 + 0.4

T

CY

/2 + 0.4

0.15

0

10

14

Output Disable Time, OE/

RST

HIGH to LOW

(3)

0

14

ns

Output Rise/Fall Times, 0.8V

~

2V

0.3

2

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QS5LV919133J | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931-50Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931-66Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931-80Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931 | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QS5LV919-100Q | 制造商:Integrated Device Technology Inc 功能描述: 制造商:QSI 功能描述: |

| QS5LV919133J | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV919133Q | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV919-133Q | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 28-Pin QSOP Tube |

| QS5LV919-133Q8 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 28-Pin QSOP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。