- 您現(xiàn)在的位置:買賣IC網 > PDF目錄361317 > QS5LV919100Q (INTEGRATED DEVICE TECHNOLOGY INC) 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER PDF資料下載

參數(shù)資料

| 型號: | QS5LV919100Q |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| 中文描述: | 5LV SERIES, PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | QSOP-28 |

| 文件頁數(shù): | 9/12頁 |

| 文件大小: | 98K |

| 代理商: | QS5LV919100Q |

9

INDUSTRIAL TEMPERATURE RANGE

QS5LV919

3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

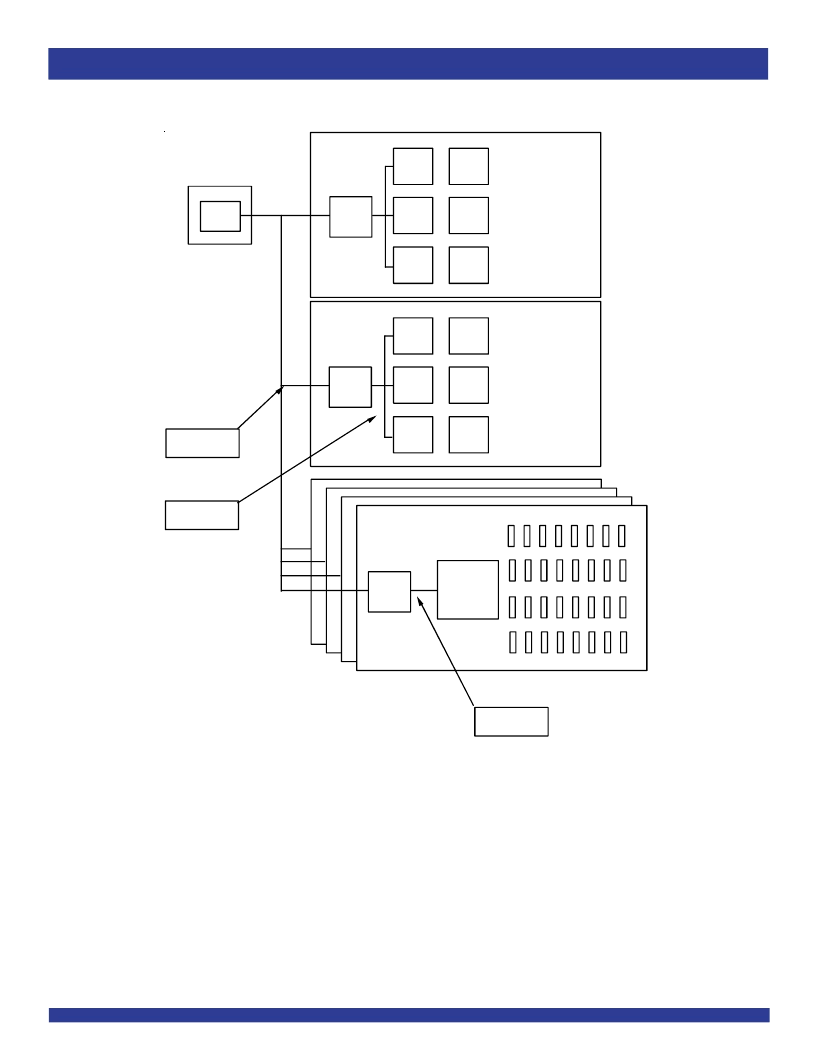

CMMU

CMMU

CPU

CMMU

CMMU

CMMU

CMMU

CMMU

CPU

CMMU

CMMU

CMMU

PLL

2f

PLL

2f

CPU

CARD

CPU

CARD

CLOCK

@f

SYSTEM

CLOCK

SOURCE

QS5LV919

QS5LV919

DISTRIBUTE

CLOCK @f

CLOCK @2f

at point of use

MEMORY

CONTROL

PLL

2f

MEMORY

CARDS

CLOCK @2f

at point of use

QS5LV919

Figure 3. Multiprocessing Application Using the QS5LV919 for Frequency Multiplication and Low Board-to-Board skew

QS5LV919 System Level Testing Functionality

When the PLL_EN pin is LOW, the PLL is bypassed and the QS5LV919 is

in low frequency "test mode". In test mode (with FREQ_SEL HIGH), the 2Q

output is inverted fromthe selected SYNC input, and the Q outputs are divide-

by-2 (negative edge triggered) of the SYNC input, and the Q/2 output is divide-

by-4 (negative edge triggered). With FREQ_SEL LOW the 2Q output is divide-

by-2 of the SYNC, the Q outputs divide-by-4, and the Q/2 output divide-by-8.

These relationships can be seen in the block diagram A recommended test

configuration would be to use SYNC0 or SYNC1 as the test clock input, and tie

PLL_EN and REF_SEL together and connect themto the test select logic.

This functionality is needed since most board-level testers run at 1 MHz or

below, and the QS5LV919 cannot lock onto that low of an input frequency. In

the test mode described above, any test frequency test can be used.

相關PDF資料 |

PDF描述 |

|---|---|

| QS5LV919133J | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931-50Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931-66Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931-80Q | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV931 | 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| QS5LV919-100Q | 制造商:Integrated Device Technology Inc 功能描述: 制造商:QSI 功能描述: |

| QS5LV919133J | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV919133Q | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

| QS5LV919-133Q | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 28-Pin QSOP Tube |

| QS5LV919-133Q8 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 28-Pin QSOP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復。