- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372062 > RGR2622 Fiber Optic “Light to Logic” Receiver with Clock Recovery PDF資料下載

參數(shù)資料

| 型號: | RGR2622 |

| 英文描述: | Fiber Optic “Light to Logic” Receiver with Clock Recovery |

| 中文描述: | 光纖“光的邏輯”接收機時鐘恢復(fù) |

| 文件頁數(shù): | 3/6頁 |

| 文件大小: | 102K |

| 代理商: | RGR2622 |

408

Functional Description

Design

The receiver contains an InGaAsP

photodetector, transimpedance

amplifier and interface amplifier

circuit, including a clock recovery

and data retiming function. It is

designed with a multimode fiber

pigtail to allow maximum

flexibility in connector options.

The interface amplifier is ac

coupled to the preamplifier

circuit.

Terminating the Outputs

The data outputs of the RGR2622

are PECL compatible. Care

should be taken to match termin-

ation impedances to the intercon-

nect to minimize reflection

effects. In order to balance the

drive currents drawn from the

RGR2622 all serial data outputs

(DATA and DATA, CLOCK and

CLOCK) should be terminated

identically, even if only one

output is used.

This will lower the power supply

noise generated by the RGR2622

and improve performance at low

optical input power levels.

Power Supplies

The RGR2622 will operate to

specifications with a single +5 V

power supply (Pin 10 grounded).

The –5 V pin bias is provided to

maintain functional compatibility

with second sources.

Circuit Layout

The RGR2622 uses very high

bandwidth circuitry to achieve its

high level of performance. Care

must be taken to ensure stable

operation. The use of ground

planes and transmission line

interconnects is required. The use

of a standard evaluation board is

highly recommended for those

users who are not familiar with

these techniques.

Signal traces should conform to

ECL design rules to prevent

reflections and ringing from

degrading performance. Useful

guidelines are contained in ECL

manufacturer design manuals.

Manufacturing

The fiber pigtail on the device

requires normal fiber handling

considerations. Care should be

taken to avoid tight bends as well

as excessive tension on the fiber

pigtail.

The allowable temperature range

for the RGR2622 is limited by the

material used in the pigtail.

Exposure to temperatures over

+85

°

C is not recommended. Low

profile sockets or hand soldering

are recommended for this part.

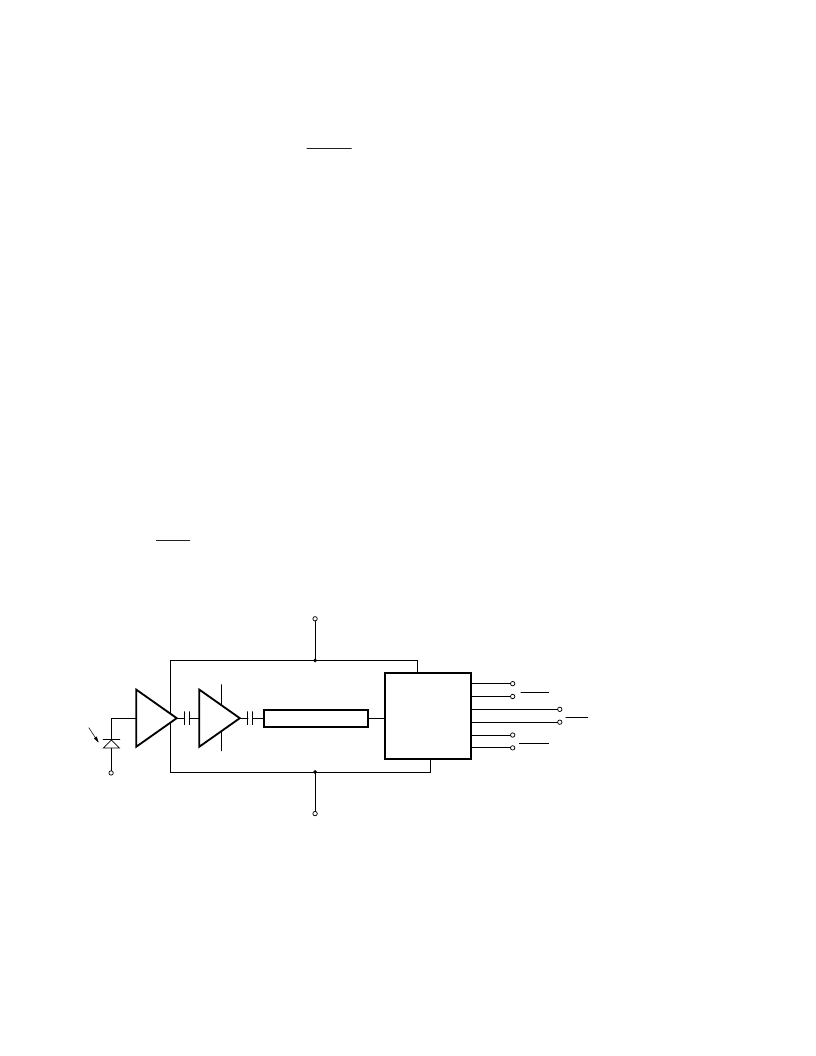

Figure 1. Block Diagram.

MID

AMP

LOW PASS FILTER

PLL

CLOCK AND

DATA RECOVERY

V

CC

(+5 V)

GND (0 V)

ALARM

ALARM

DATA

DATA

CLOCK

CLOCK

V

NEG

(-5 V OR GND)

TI

AMP

+5 V

0 V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RGR2622-DN | Fiber Optic “Light to Logic” Receiver with Clock Recovery |

| RGR2622-FP | Fiber Optic “Light to Logic” Receiver with Clock Recovery |

| RGR2622-SC | Fiber Optic “Light to Logic” Receiver with Clock Recovery |

| RGR2622-ST | Fiber Optic “Light to Logic” Receiver with Clock Recovery |

| RH129AH | Voltage Reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RGR2622-DN | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fiber Optic “Light to Logic” Receiver with Clock Recovery |

| RGR2622-FP | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fiber Optic “Light to Logic” Receiver with Clock Recovery |

| RGR2622-SC | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fiber Optic “Light to Logic” Receiver with Clock Recovery |

| RGR2622-ST | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fiber Optic “Light to Logic” Receiver with Clock Recovery |

| RGR5HXB37C15 | 制造商:VECTRON 制造商全稱:Vectron International, Inc 功能描述:Temperature Compensated Crystal Oscillators |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。