- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373294 > RM5271-225S 64-Bit Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | RM5271-225S |

| 英文描述: | 64-Bit Microprocessor |

| 中文描述: | 64位微處理器 |

| 文件頁數(shù): | 14/24頁 |

| 文件大?。?/td> | 387K |

| 代理商: | RM5271-225S |

14

RM5271 Microprocessor, Document Rev. 1.3

Quantum Effect Devices

www.qedinc.com

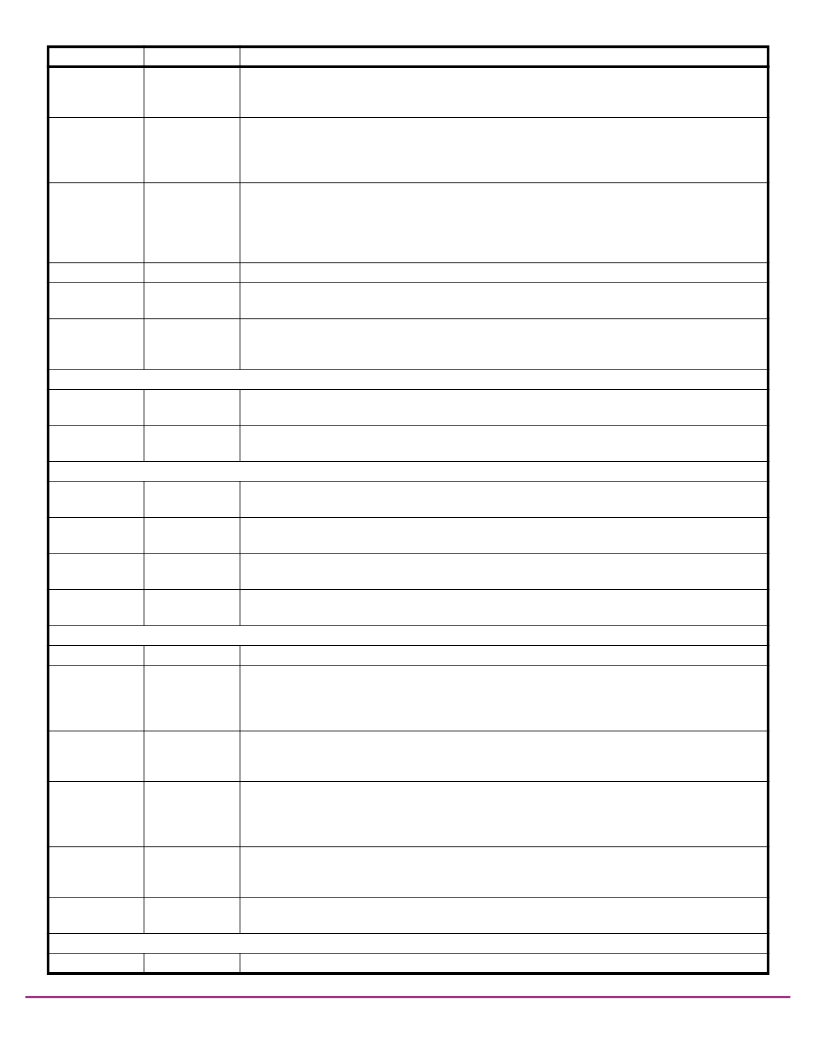

ScMatch

Input

Secondary Cache Tag Match

This signal is asserted by the cache Tag RAM’s when a match occurs between the value on its data

inputs and the contents of its RAM at the value on its address inputs.

ScTCE*

Output

Secondary Cache Tag RAM Chip Enable

When asserted this signal will cause either a probe or a write of the Tag RAM’s depending on the

state of the Tag RAM’s write enable signal. This signal is monitored by the external agent and indi-

cates to it that a secondary cache access is occurring.

ScTDE*

Output

Secondary Cache Tag RAM Data Enable

When asserted this signal causes the value on the data inputs of the Tag RAM to be latched into

the RAM. If a refill of the RAM is necessary, this latched value will be written into the Tag RAM

array. Latching the Tag allows a shared address/data bus to be used without incurring a penalty to

re-present the Tag during the refill sequence.

ScTOE*

Output

When asserted this signal causes the Tag RAM’s to drive data onto their I/O pins.

ScWord(1:0)

Input/Output

Secondary Cache Double Word Index

Driven by the processor on cache hits and by the external agent on cache miss refills.

ScValid

Input/Output

Secondary Cache Valid

This signal is driven by the processor as appropriate to make a cache line valid or invalid. On Tag

read operations the Tag RAM will drive this signal to indicate the line state.

Interrupt interface:

Int*(5:0)

Input

Interrupt

Six general processor interrupts, bit-wise ORed with bits 5:0 of the interrupt register.

NMI*

Input

Non-maskable interrupt

Non-maskable interrupt, ORed with bit 6 of the interrupt register.

JTAG interface:

JTDI

Input

JTAG data in

JTAG serial data in.

JTCK

Input

JTAG clock input

JTAG serial clock input.

JTDO

Output

JTAG data out

JTAG serial data out.

JTMS

Input

JTAG command

JTAG command signal, signals that the incoming serial data is command data.

Initialization interface:

BigEndian

Input

Allows the system to change the processor addressing mode without rewriting the mode ROM.

VccOK

Input

Vcc is OK

When asserted, this signal indicates to the RM5270 that the 3.3V power supply has been above

3.0V for more than 100 milliseconds and will remain stable. The assertion of VccOk initiates the

reading of the boot-time mode control serial stream.

ColdReset*

Input

Cold reset

This signal must be asserted for a power on reset or a cold reset. ColdReset must be de-asserted

synchronously with SysClock.

Reset*

Input

Reset

This signal must be asserted for any reset sequence. It may be asserted synchronously or asyn-

chronously for a cold reset, or synchronously to initiate a warm reset. Reset must be de-asserted

synchronously with SysClock.

ModeClock

Output

Boot mode clock

Serial boot-mode data clock output at the system clock frequency divided by two hundred and fifty

six.

ModeIn

Input

Boot mode data in

Serial boot-mode data input.

Reserved Pins

Reserved

Input/Output

Reserved for RM7000 compatibility

Pin Name

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RM5271-250S | 64-Bit Microprocessor |

| RM5271-266S | 64-Bit Microprocessor |

| RM5534T | Voltage-Feedback Operational Amplifier |

| RC5534AD | Voltage-Feedback Operational Amplifier |

| RC5534D | Voltage-Feedback Operational Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RM5271-250S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5271-266S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5271-300S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5271-350S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM528-R2 | 制造商:Black Box Corporation 功能描述:Panhead Screws, 10-32, 5/8", , 20-Pack |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。