- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373294 > RM5271-225S 64-Bit Microprocessor PDF資料下載

參數(shù)資料

| 型號: | RM5271-225S |

| 英文描述: | 64-Bit Microprocessor |

| 中文描述: | 64位微處理器 |

| 文件頁數(shù): | 3/24頁 |

| 文件大小: | 387K |

| 代理商: | RM5271-225S |

Quantum Effect Devices

www.qedinc.com

RM5271 Microprocessor, Document Rev. 1.3

3

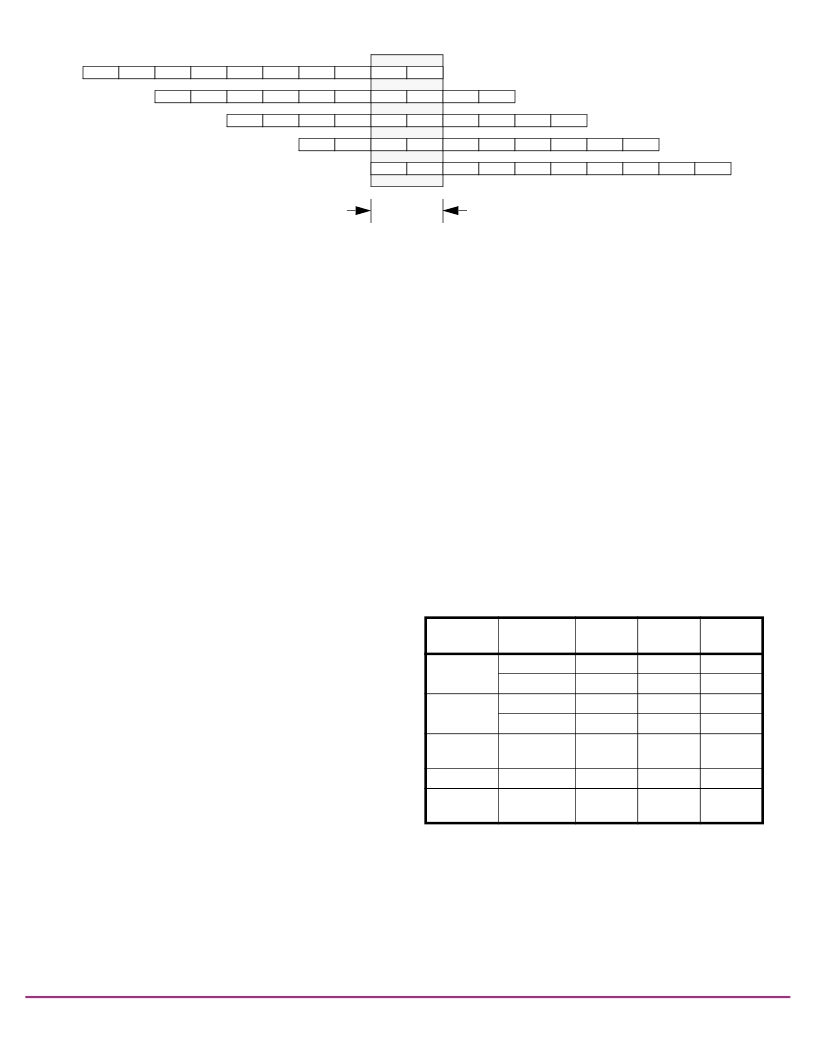

Figure 2 Pipeline

Integer Unit

The RM5271 implements the MIPS IV Instruction Set

Architecture, and is therefore fully upward compatible with

applications that run on processors implementing the ear-

lier generation MIPS I-III instruction sets. Additionally, the

RM5271 includes two implementation-specific instructions

not found in the baseline MIPS IV ISA but that are useful in

the embedded market place. These instructions are integer

multiply-accumulate (MAD) and 3-operand integer multiply

(MUL).

The RM5271 integer unit includes thirty-two general pur-

pose 64-bit registers, a load/store architecture with single

cycle ALU operations (add, sub, logical, shift) and an

autonomous multiply/divide unit. Additional register

resources include: the HI/LO result registers for the two-

operand integer multiply/divide operations, and the pro-

gram counter (PC).

Register File

The RM5271 has thirty-two general purpose registers with

register location 0 (r0) hard wired to a zero value. These

registers are used for scalar integer operations and

address calculation. The register file has two read ports

and one write port and is fully bypassed to minimize opera-

tion latency in the pipeline.

ALU

The RM5271 ALU consists of an integer adder/subtractor, a

logic unit, and a shifter. The adder performs address calcu-

lations in addition to arithmetic operations. The logic unit

performs all logical and zero shift data moves. The shifter

performs shifts and store alignment operations. Each of

these units is optimized to perform all operations in a single

processor cycle.

Integer Multiply/Divide

The RM5271 has a dedicated integer multiply/divide unit

optimized for high-speed multiply and multiply-accumulate

operations. Table 1 shows the performance of the multiply/

divide unit on each operation.

The baseline MIPS IV ISA specifies that the results of a

multiply or divide operation be placed in the Hi and Loreg-

isters. These values can then be transferred to the general

purpose register file using the Move-from-Hi and Move-

from-Lo (MFHI/MFLO) instructions.

In addition to the baseline MIPS IV integer multiply instruc-

tions, the RM5271 also implements the 3-operand multiply

instruction, MUL. This instruction specifies that the multiply

I0

I1

I2

I3

I4

2I

1I

1R

2R

1A

2A

1D

2D

1W

2W

2I

1I

1R

2R

1A

2A

1D

2D

1W

2W

2I

1I

1R

2R

1A

2A

1D

2D

1W

2W

2I

1I

1R

2R

1A

2A

1D

2D

1W

2W

2I

1I

1R

2R

1A

2A

1D

2D

1W

2W

one cycle

1I-1R:

2I:

2R:

1A:

1A:

2A-2D:

1A-2A:

1D:

2W:

2A:

Instruction cache access

Instruction virtual to physical address translation

Register file read, Bypass calculation, Instruction decode, Branch address calculation

Issue or slip decision, Branch decision

Data virtual address calculation

Integer add, logical, shift

Store Align

Data cache access and load align

Data virtual to physical address translation

Register file write

Table 1:

Integer Multiply/Divide Operations

Opcode

MULT/U,

MAD/U

Operand

Size

16 bit

Latency

3

Repeat

Rate

Stall

Cycles

2

0

32 bit

4

3

0

MUL

16 bit

3

2

1

32 bit

4

3

2

DMULT,

DMULTU

any

7

6

0

DIV, DIVD

any

36

36

0

DDIV,

DDIVU

any

68

68

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RM5271-250S | 64-Bit Microprocessor |

| RM5271-266S | 64-Bit Microprocessor |

| RM5534T | Voltage-Feedback Operational Amplifier |

| RC5534AD | Voltage-Feedback Operational Amplifier |

| RC5534D | Voltage-Feedback Operational Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RM5271-250S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5271-266S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5271-300S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5271-350S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM528-R2 | 制造商:Black Box Corporation 功能描述:Panhead Screws, 10-32, 5/8", , 20-Pack |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。