- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376313 > RM7000-225S (PMC-Sierra, Inc.) RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released PDF資料下載

參數(shù)資料

| 型號(hào): | RM7000-225S |

| 廠商: | PMC-Sierra, Inc. |

| 英文描述: | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| 中文描述: | RM7000⑩微處理器與片上二級(jí)高速緩存數(shù)據(jù)發(fā)布 |

| 文件頁(yè)數(shù): | 36/54頁(yè) |

| 文件大小: | 901K |

| 代理商: | RM7000-225S |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer

’

s Internal Use

Document ID: PMC-2002175, Issue 1

36

RM7000

Microprocessor with On-Chip Secondary Cache Datasheet

Released

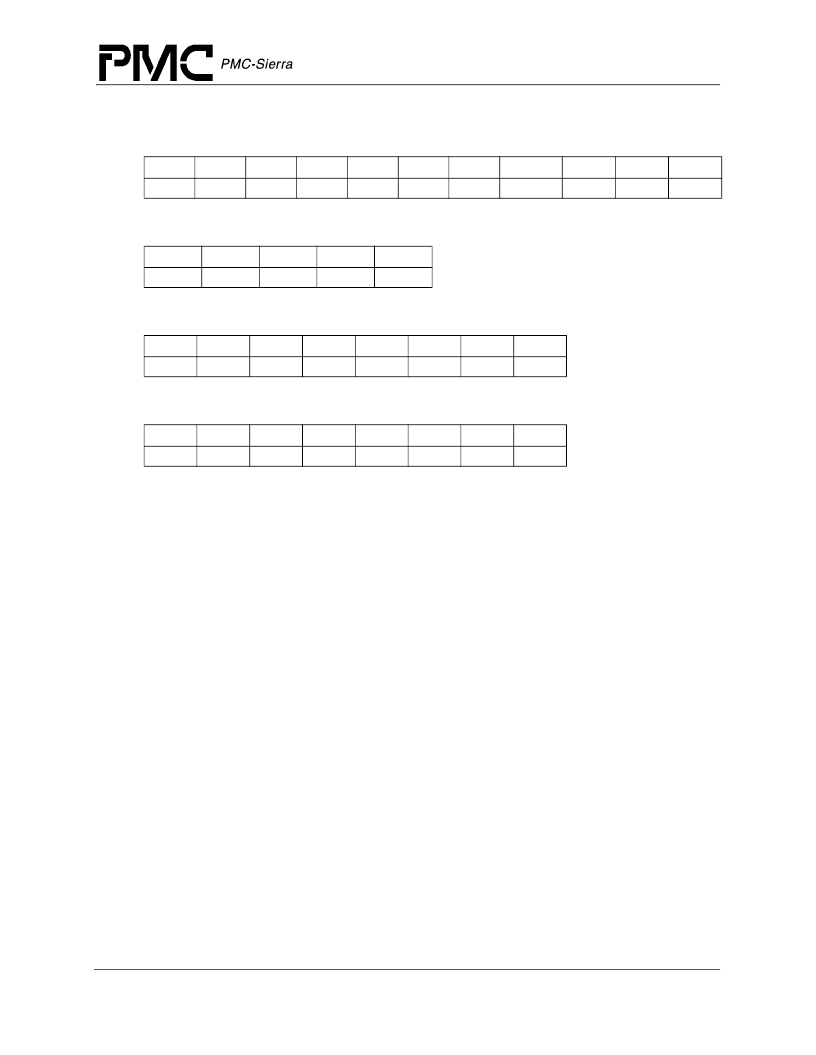

Table 11 Cause Register

Table 12 Interrupt Control Register

Table 13 IPLLO Register

Table 14 IPLHI Register

These two registers contain a four-bit field corresponding to each interrupt thereby allowing each

interrupt to be programmed with a priority level from 0 to 13 inclusive. The priorities can be set in

any manner including having all the priorities set exactly the same. Priority 0 is the highest level

and priority 15 the lowest. The format of the priority level registers is shown in Table 13 and Table

14 above. The priority level registers are located in the coprocessor 0 control register space. For

further details about the control space see the section describing coprocessor 0.

In addition to programmable priority levels, the RM7000 also permits the spacing between

interrupt vectors to be programmed. For example, the minimum spacing between two adjacent

vectors is 0x20 while the maximum is 0x200. This programmability allows the user to either set up

the vectors as jumps to the actual interrupt routines or, if interrupt latency is paramount, to include

the entire interrupt routine at the vector. Table 15 illustrates the complete set of vector spacing

selections along with the coding as required in the

Interrupt Control

register bits 4:0.

In general, the active interrupt priority combined with the spacing setting generates a vector offset

which is then added to the interrupt base address of 0x200 to generate the interrupt exception

offset. This offset is then added to the exception base to produce the final interrupt vector address.

31

BD

30

0

29,28

CE

27

0

26

W2

25

W1

24

IV

23..8

IP[15..0]

7

0

6..2

EXC

0,1

0

31..16

0

15..8

IM[15..8]

7

TE

6..5

0

4..0

Spacing

31..28

IPL7

27..24

IPL6

23..20

IPL5

19..16

IPL4

15..12

IPL3

11..8

IPL2

7..4

IPL1

3..0

IPL0

31..28

0

27..24

0

23..20

IPL13

19..16

IPL12

15..12

IPL11

11..8

IPL10

7..4

IPL9

3..0

IPL8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RM7000-250S | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7000-250T | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7000-263S | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7000-266T | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7000-300S | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RM7000-250S | 制造商:QED 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA |

| RM7000263S | 制造商:QED 功能描述:* |

| RM7000-263S | 制造商:QED 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA 制造商:Quantum Effect Design 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA |

| RM7000-266T | 制造商:QED 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA |

| RM7000-300T | 制造商:QED 功能描述: 制造商:QED 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。