- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376330 > S12FTS128KV2D (Motorola, Inc.) MC9S12DT128 Device User Guide V02.09 PDF資料下載

參數(shù)資料

| 型號: | S12FTS128KV2D |

| 廠商: | Motorola, Inc. |

| 英文描述: | MC9S12DT128 Device User Guide V02.09 |

| 中文描述: | MC9S12DT128設(shè)備的用戶手冊V02.09 |

| 文件頁數(shù): | 117/138頁 |

| 文件大小: | 2083K |

| 代理商: | S12FTS128KV2D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁當前第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁

MC9S12DT128 Device User Guide — V02.09

117

A.5 Reset, Oscillator and PLL

This section summarizes the electrical characteristics of the various startup scenarios for Oscillator and

Phase-Locked-Loop (PLL).

A.5.1 Startup

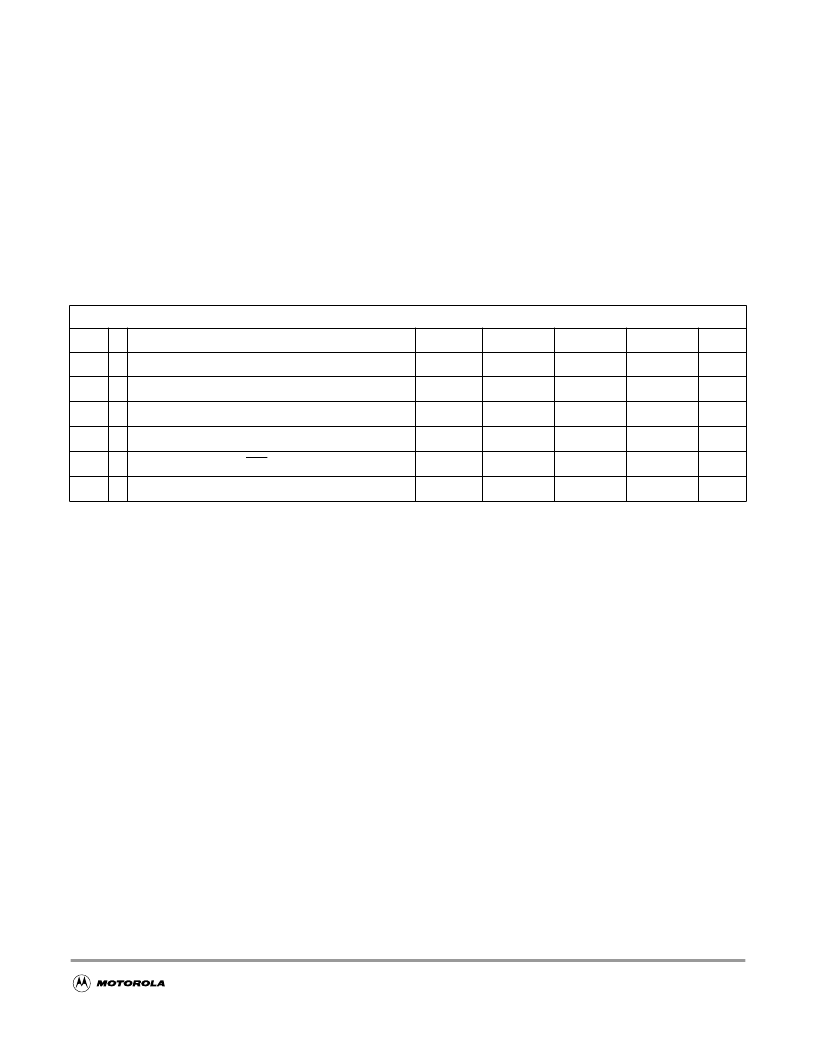

Table A-14

summarizes several startup characteristics explained in this section. Detailed description of

the startup behavior can be found in the Clock and Reset Generator (CRG) Block User Guide.

Table A-14 Startup Characteristics

A.5.1.1 POR

The release level V

PORR

and the assert level V

PORA

are derived from the V

DD

Supply. They are also valid

ifthedeviceispoweredexternally.AfterreleasingthePORresettheoscillatorandtheclockqualitycheck

are started. If after a time t

CQOUT

no valid oscillation is detected, the MCU will start using the internal self

clock. The fastest startup time possible is given by n

uposc

.

A.5.1.2 SRAM Data Retention

Provided an appropriate external reset signal is applied to the MCU, preventing the CPU from executing

codewhenVDD5isoutofspecificationlimits,theSRAMcontentsintegrityisguaranteedifafterthereset

the PORF bit in the CRG Flags Register has not been set.

A.5.1.3 External Reset

When external reset is asserted for a time greater than PW

RSTL

the CRG module generates an internal

reset, and the CPU starts fetching the reset vector without doing a clock quality check, if there was an

oscillation before reset.

A.5.1.4 Stop Recovery

Out of STOP the controller can be woken up by an external interrupt. A clock quality check as after POR

is performed before releasing the clocks to the system.

Conditions are shown in

Table A-4

unless otherwise noted

Num C

Rating

Symbol

Min

Typ

Max

Unit

1

T POR release level

V

PORR

2.07

V

2

T POR assert level

V

PORA

0.97

V

3

D Reset input pulse width, minimum input time

PW

RSTL

2

t

osc

4

D Startup from Reset

n

RST

192

196

n

osc

5

D Interrupt pulse width, IRQ edge-sensitive mode

PW

IRQ

20

ns

6

D Wait recovery startup time

t

WRS

14

t

cyc

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S12MEBIV3 | MC9S12DT128 Device User Guide V02.09 |

| S12MEBIV3D | MC9S12DT128 Device User Guide V02.09 |

| S12SCIV2 | MC9S12DT128 Device User Guide V02.09 |

| S12SCIV2D | MC9S12DT128 Device User Guide V02.09 |

| S12VREGV1 | MC9S12DT128 Device User Guide V02.09 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S12FTS128KVD | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:128k byte Flash (Non-Volatile) Memory |

| S12FTS256KV2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Automotive applications |

| S12FTS256KV2/D | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Device User Guide V01.18 |

| S12FTS64KV1D | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MC9S12DJ64 Device User GUide V01.17 |

| S12G | 功能描述:整流器 400V 12A Std. Recovery RoHS:否 制造商:Vishay Semiconductors 產(chǎn)品:Standard Recovery Rectifiers 配置: 反向電壓:100 V 正向電壓下降: 恢復時間:1.2 us 正向連續(xù)電流:2 A 最大浪涌電流:35 A 反向電流 IR:5 uA 安裝風格:SMD/SMT 封裝 / 箱體:DO-221AC 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。