- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25640 > S1C60N05D0A0100 MICROCONTROLLER, UUC53 PDF資料下載

參數(shù)資料

| 型號(hào): | S1C60N05D0A0100 |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | MICROCONTROLLER, UUC53 |

| 封裝: | DIE-53 |

| 文件頁(yè)數(shù): | 51/95頁(yè) |

| 文件大小: | 736K |

| 代理商: | S1C60N05D0A0100 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)當(dāng)前第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)

58

7674F–AVR–09/09

ATmega164P/324P/644P

9.3.2

WDTCSR – Watchdog Timer Control Register

Bit 7 - WDIF: Watchdog Interrupt Flag

This bit is set when a time-out occurs in the Watchdog Timer and the Watchdog Timer is config-

ured for interrupt. WDIF is cleared by hardware when executing the corresponding interrupt

handling vector. Alternatively, WDIF is cleared by writing a logic one to the flag. When the I-bit in

SREG and WDIE are set, the Watchdog Time-out Interrupt is executed.

Bit 6 - WDIE: Watchdog Interrupt Enable

When this bit is written to one and the I-bit in the Status Register is set, the Watchdog Interrupt is

enabled. If WDE is cleared in combination with this setting, the Watchdog Timer is in Interrupt

Mode, and the corresponding interrupt is executed if time-out in the Watchdog Timer occurs.

If WDE is set, the Watchdog Timer is in Interrupt and System Reset Mode. The first time-out in

the Watchdog Timer will set WDIF. Executing the corresponding interrupt vector will clear WDIE

and WDIF automatically by hardware (the Watchdog goes to System Reset Mode). This is use-

ful for keeping the Watchdog Timer security while using the interrupt. To stay in Interrupt and

System Reset Mode, WDIE must be set after each interrupt. This should however not be done

within the interrupt service routine itself, as this might compromise the safety-function of the

Watchdog System Reset mode. If the interrupt is not executed before the next time-out, a Sys-

tem Reset will be applied.

Bit 4 - WDCE: Watchdog Change Enable

This bit is used in timed sequences for changing WDE and prescaler bits. To clear the WDE bit,

and/or change the prescaler bits, WDCE must be set.

Once written to one, hardware will clear WDCE after four clock cycles.

Bit 3 - WDE: Watchdog System Reset Enable

WDE is overridden by WDRF in MCUSR. This means that WDE is always set when WDRF is

set. To clear WDE, WDRF must be cleared first. This feature ensures multiple resets during con-

ditions causing failure, and a safe start-up after the failure.

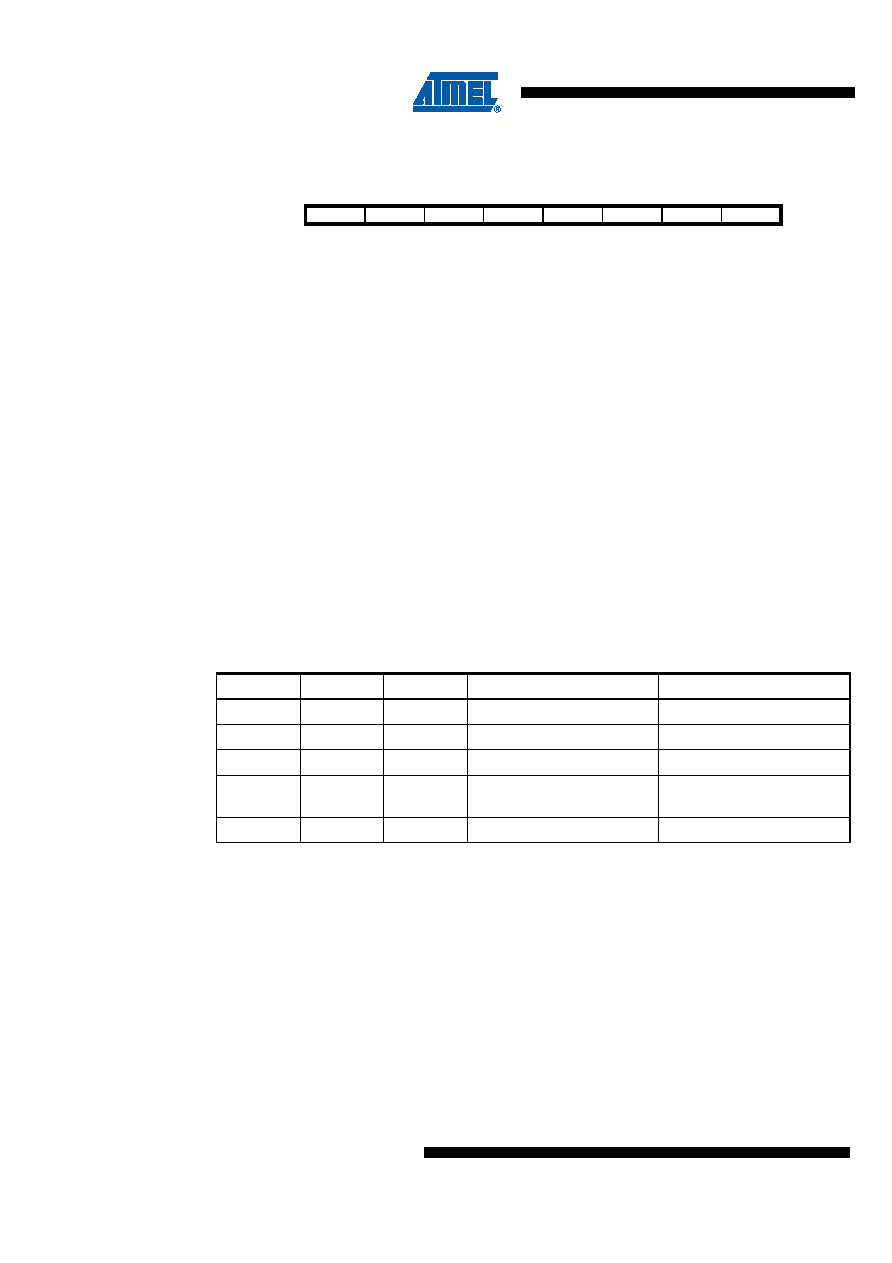

Bit

76543210

WDIF

WDIE

WDP3

WDCE

WDE

WDP2

WDP1

WDP0

WDTCSR

Read/Write

R/W

Initial Value

0000

X

000

Table 9-1.

Watchdog Timer Configuration

WDTON

WDE

WDIE

Mode

Action on Time-out

0

Stopped

None

0

1

Interrupt Mode

Interrupt

0

1

0

System Reset Mode

Reset

011

Interrupt and System Reset

Mode

Interrupt, then go to System

Reset Mode

1

x

System Reset Mode

Reset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S1C621A0F0A0100 | MICROCONTROLLER, PQFP80 |

| S1C63158D0A010P | 4-BIT, FLASH, 4 MHz, MICROCONTROLLER, UUC53 |

| S1C7XXXF00E199 | 16-BIT, 90 MHz, RISC MICROCONTROLLER, PQFP |

| S2041 | PHOTO TRANSISTOR DETECTOR |

| S3P44R10 | TRIGGER OUTPUT SOLID STATE RELAY, 4000 V ISOLATION-MAX |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S1C60N08 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C60N16 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C60R08 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63004 | 制造商:EPSON 制造商全稱:EPSON 功能描述:CMOS 4-bit Single Chip Microcontroller |

| S1C63008 | 制造商:EPSON 制造商全稱:EPSON 功能描述:CMOS 4-bit Single Chip Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。