- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368612 > S5N8947X (SAMSUNG SEMICONDUCTOR CO. LTD.) MCU for ADSL/Cable Modem PDF資料下載

參數(shù)資料

| 型號: | S5N8947X |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | MCU for ADSL/Cable Modem |

| 中文描述: | 單片機為ADSL / Cable Modem的 |

| 文件頁數(shù): | 16/49頁 |

| 文件大?。?/td> | 407K |

| 代理商: | S5N8947X |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

S5N8947 (ADSL/Cable Modem MCU)

ELECTRONICS

MagIC Team

Page : 16

SAMSUNG ELECTRONICS

5. O

PERATION

D

ESCRIPTION

5.1. CPU Core Overview

The S5N8947 CPU core is the ARM7TDMI processor, a general purpose, 32-bit microprocessor

developed by Advanced RISC Machines, Ltd. (ARM). The core's architecture is based on Reduced

Instruction Set Computer (RISC) principles. The RISC architecture makes the instruction set and its

related decoding mechanisms simpler and more efficient than those with microprogrammed Complex

Instruction Set Computer (CISC) systems. The resulting benefit is high instruction throughput and

impressive real-time interrupt response. Pipelining is also employed so that all components of the

processing and memory systems can operate continuously. The ARM7TDMI has a 32-bit address bus.

An important feature of the ARM7TDMI processor, and one which differentiates it from the ARM7

processor, is a unique architectural strategy called THUMB. The THUMB strategy is an extension of the

basic ARM architecture and consists of 36 instruction formats. These formats are based on the standard

32-bit ARM instruction set, but have been re-coded using 16-bit wide opcodes.

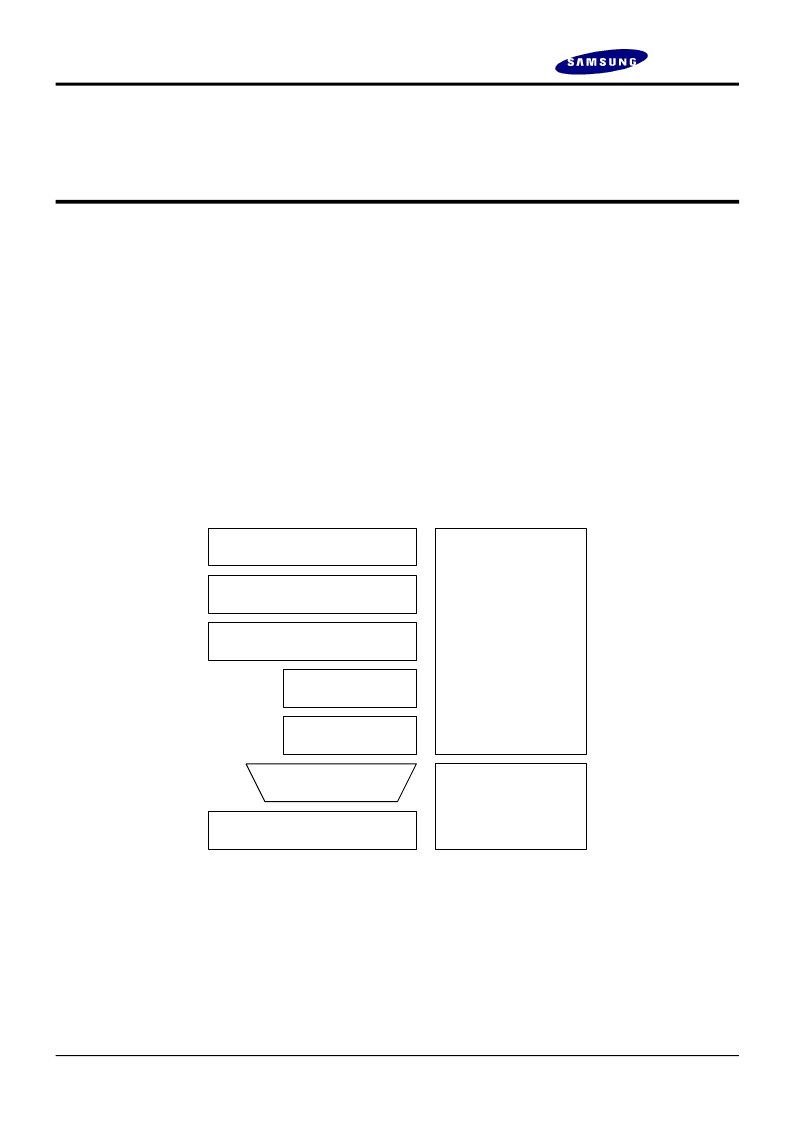

Address

Register

Address

Incrementer

Register Bank

Multiplier

Barrel

Shifter

32-BIT ALU

Write Data

Register

Instruction

Decoder and

Logic Controll

Instruction

Pipeline and Read

Data Register

Figure 3 ARM7TDMI Core Block Diagram

Because THUMB instructions are one-half the bit width of normal ARM instructions, they produce very high-density

code. When a THUMB instruction is executed, its 16-bit opcode is decoded by the processor into its equivalent instruction in

the standard ARM instruction set. The ARM core then processes the 16-bit instruction as it would a normal 32-bit

instruction. In other words, the THUMB architecture gives 16-bit systems a way to access the 32-bit performance of the ARM

core without incurring the full overhead of 32-bit processing. Because the ARM7TDMI core can execute both standard 32-bit

ARM instructions and 16-bit THUMB instructions, it lets you mix routines of THUMB instructions and ARM code in the

same address space. In this way, you can adjust code size and performance, routine by routine, to find the best programming

solution for a specific application.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S5N8950 | G.dmt ADSL Transceiver for CO and CPE |

| S5N8951 | G.dmt ADSL Analog Front End IC |

| S5N8951X | G.dmt ADSL Analog Front End IC |

| S5N8952 | ADSL Transceiver for NIC |

| S5N8952X | ADSL Transceiver for NIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S5N8950 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:G.dmt ADSL Transceiver for CO and CPE |

| S5N8951 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:G.dmt ADSL Analog Front End IC |

| S5N8951X | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:G.dmt ADSL Analog Front End IC |

| S5N8952 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:ADSL Transceiver for NIC |

| S5N8952X | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:ADSL Transceiver for NIC |

發(fā)布緊急采購,3分鐘左右您將得到回復。