- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372108 > SA8027W (NXP SEMICONDUCTORS) 2.5 GHz low voltage, low power RF fractional-N/IF integer frequency synthesizer PDF資料下載

參數(shù)資料

| 型號: | SA8027W |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | XO, clock |

| 英文描述: | 2.5 GHz low voltage, low power RF fractional-N/IF integer frequency synthesizer |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 2500 MHz, PQCC24 |

| 封裝: | PLASTIC, BCC-24 |

| 文件頁數(shù): | 11/22頁 |

| 文件大?。?/td> | 231K |

| 代理商: | SA8027W |

Philips Semiconductors

Product data

SA8027

2.5 GHz low voltage, low power

RF fractional-N/IF integer frequency synthesizer

2001 Aug 21

11

1.7

The PHP and PHI charge pumps are driven by the main phase

detector, while the PHA charge pump is driven by the auxiliary

phase detector. The I

SET

value (refer to Table 1) is determined by

the external resistor attached to the R

SET

pin.

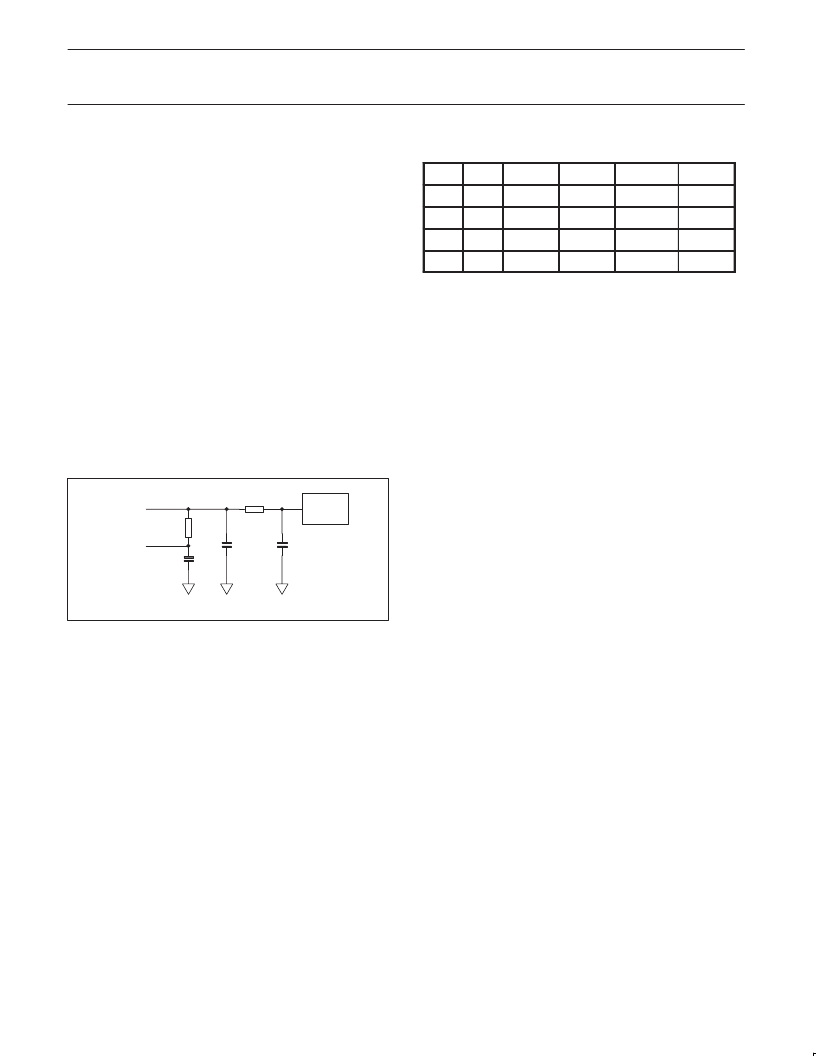

Charge Pumps

The charge pump, by default, will automatically go into speed-up

mode (which can deliver up to 15*I

SET

for PHP_SU, and 36*I

SET

for

PHI), based on the strobe pulse width following the A word, to

reduce switching speed for large tuning voltage steps (i.e., large

frequency steps). Figure 10 shows the recommended passive loop

filter configuration. Note: This charge pump architecture eliminates

the need for added active switches and reduces external component

count. Furthermore, the programmable charge pump gains provide

some programmability to the loop filter bandwidth.

The duration of speed-up mode is determined by the strobe pulse

width following the A word. Recommended optimal strobe width is

equal to the total loop filter capacitance charge time from state 1 to

state 2. The strobe width must not exceed this charge time. The

strobe width is controlled by the CPU (

×

number of clock cycles).

In addition, charge pumps will stay in speed-up mode continuously

while Tspu = 1 (in D word). The speed-up mode can also be

disabled by programming T

dis-spu

= 1 (in D word).

SR02356

VCO

C3

C2

R2

C1

R1

PHP[PHP–SU]

PHI

Figure 10.

Typical passive 3-pole loop filter

Table 1. Main and auxiliary charge pump currents

CP1

CP0

I

PHA

I

PHP

I

PHP–SU

I

PHI

0

0

1.5xl

SET

3xI

SET

15xl

SET

36xl

SET

0

1

0.5xl

SET

1xl

SET

5xl

SET

12xl

SET

1

0

1.5xl

SET

3xl

SET

15xl

SET

0

1

1

0.5xl

SET

1xl

SET

5xl

SET

0

NOTES:

1. I

SET

= V

SET

/R

SET

: bias current for charge pumps.

2. CP1 is used to disable the PHI pump, I

PHP–SU

is the total current

at pin PHP during speed up condition.

1.8

The output LOCK maintains a logic ‘1’ when the auxiliary phase

detector (AND/ORed) with the main phase detector indicates a lock

condition. The lock condition for the main and auxiliary synthesizers

is defined as a phase difference of less than

frequency at the input REF

in+, –

. One counter can fulfill the lock

condition when the other counter is powered down. Out of lock

(logic ‘0’) is indicated when both counters are powered down.

Lock Detect

1 period of the

1.9

The power-down signal can be either hardware (PON) or software

(PD). The PON signal is exclusively ORed with the PD bits in

B-word. If PON = 0, then the part is powered up when PD = 1. PON

can be used to invert the polarity of the software bit PD. When the

synthesizer is reactivated after power-down, the main and reference

dividers are synchronized to avoid possibility of random phase

errors on power-up.

Power-down mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SA8028 | 2.5 GHz sigma delta fractional-N / 760 MHz IF integer frequency synthesizers |

| SA8028W | ECONOLINE: RB & RA - Dual Output from a Single Input Rail- Power Sharing on Output- Industry Standard Pinout- 1kVDC & 2kVDC Isolation- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 85% |

| SA90-0001 | Vector Modulator, 1.94 to 2.24 GHz |

| SA90-0001-DC000 | Dual Linear Driver for Vector Modulators |

| SA90-0001TR | Vector Modulator, 1.94 to 2.24 GHz |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SA8028 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2.5 GHz sigma delta fractional-N / 760 MHz IF integer frequency synthesizers |

| SA8028W | 功能描述:鎖相環(huán) - PLL 2.5GHZ 760MHZ PLL SYNTHESIZER RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| SA8028W,518 | 功能描述:時鐘合成器/抖動清除器 2.5GHZ 760MHZ PLL RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SA8028W,557 | 功能描述:鎖相環(huán) - PLL 2.5GHZ 760MHZ PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| SA8028WGE | 功能描述:IC PLL FREQ SYNTHESIZER 24-HBCC RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發(fā)生器,PLL,頻率合成器 系列:- 標(biāo)準(zhǔn)包裝:39 系列:- 類型:* PLL:帶旁路 輸入:時鐘 輸出:時鐘 電路數(shù):1 比率 - 輸入:輸出:1:10 差分 - 輸入:輸出:是/是 頻率 - 最大:170MHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:* 封裝/外殼:* 供應(yīng)商設(shè)備封裝:* 包裝:* |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。