- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372109 > SAA4952WP (NXP SEMICONDUCTORS) Memory controller PDF資料下載

參數(shù)資料

| 型號(hào): | SAA4952WP |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 消費(fèi)家電 |

| 英文描述: | Memory controller |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC44 |

| 封裝: | PLASTIC, SOT-187, LCC-44 |

| 文件頁(yè)數(shù): | 17/32頁(yè) |

| 文件大?。?/td> | 159K |

| 代理商: | SAA4952WP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

1997 Jun 10

Philips Semiconductors

Objective specification

Memory controller

SAA4952WP

HVCD

The memory controller supplies a display related output

which can generate, depending on the microcontroller

initialization, three different signals. The desired mode is

activated via microcontroller register MODE1 (control bits

SD0 and SD1).

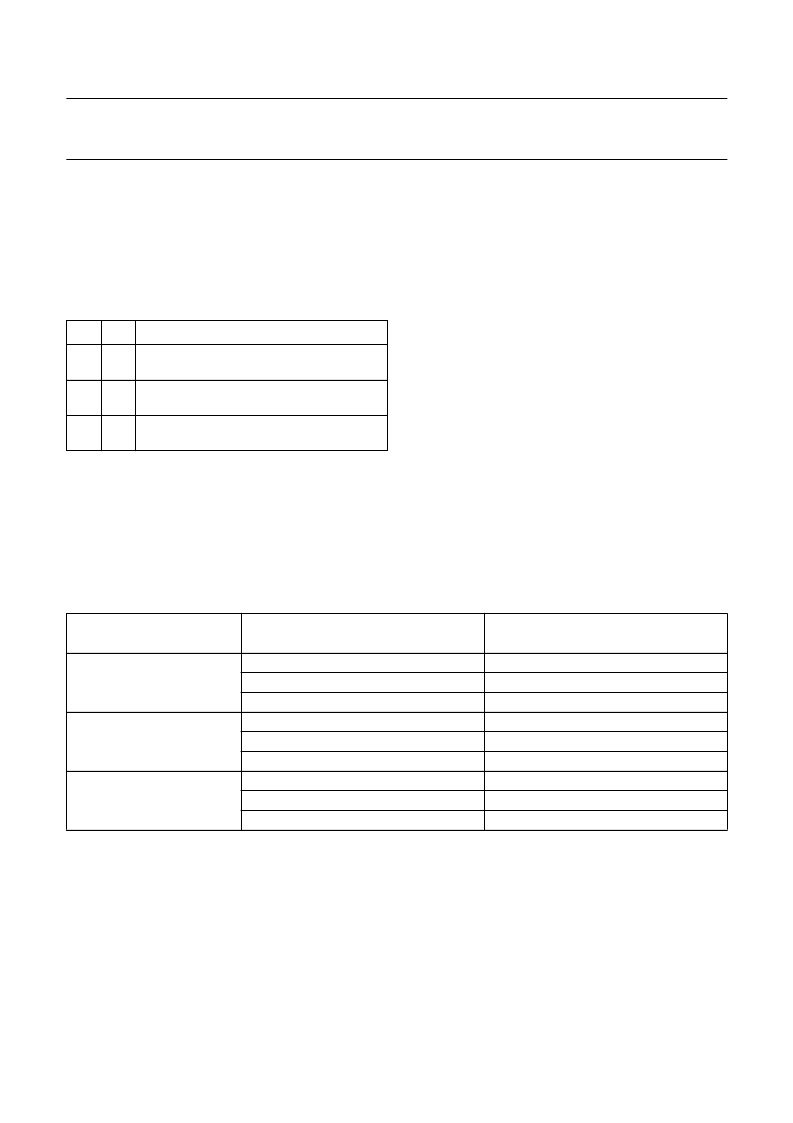

Table 14

Mode setting of SAA4952WP output HVCD

IE2

This output signal is used as data input enable for

memory 2. A logic HIGH level on this output pin enables

the data information to be written to field memory 2.

SD1 SD0

MODE OF OUTPUT PIN 17

0

0

horizontal output signal HD; programmable

via HDSTA and HDSTO

vertical output signal VD; programmable via

VDSTA and VDSTO

composite output signal HVCD; logical

AND connection of HD and VD

0

1

1

X

RE1

The output RE1 is the read enable signal for field

memory 1. A HIGH level enables the picture data to be

read from the memory. RE1 is a composite signal and

includes the horizontal read enable timing (HRE) and the

vertical read enable timing (VRE). It is possible to delay the

horizontal timing of RE1 by up to three display clock

pulses. The horizontal timing of RE1 and RE2 is equal.

RE2

The output RE2 is the read enable signal for field

memory 2. A HIGH level enables the picture data to be

read from memory. RE2 is a composite signal and includes

the horizontal read enable timing (HRE) and the vertical

read enable timing (VRE2). The horizontal timing of RE2

can be delayed by up to three display clock pulses.

The new memory controller supplies two completely

independent VRE signals, VRE1 and VRE2. VRE1 is not

generated as an adjustable delay of VRE2 as in the

SAA4951WP.

Table 15

Programming range of horizontal display signals (BLND, HRE, HWE2, HD and HVSP1 to HVSP4); see Fig.6

Nr (programmed start (rise) value of corresponding signal) not equal Nf (programmed stop (fall) value of corresponding

signal).

Notes

1.

2.

HVSP

n

= HVSP1 to HVSP4.

N: programmed value of HVSP pulse.

LLD equals LLDFL for 27 MHz display in the three-clock system.

LLD input is not used in the two-clock mode (internally switched to LLDFL input).

The programmed values include the MSB settings contained in HDMSB.

ACQUISITION FREQUENCY

(MHz)

TIMING EQUATIONS

PROGRAMMING RANGE

27

HDSP

r

= (2Nr + 2)LLD

HDSP

f

= (2Nf + 2)LLD

HVSP

n(1)

= (4N

(2)

+ 2)LLD

HDSP

r

= (2Nr + 2)LLD

HDSP

f

= (2Nf + 2)LLD

HVSP

n(1)

= (4N

(2)

+ 2)LLD

HDSP

r

= (4Nr + 4)LLD

HDSP

f

= (4Nf + 4)LLD

HVSP

n(1)

= (8N

(2)

+ 4)LLD

0

≤

Nr < 431

0

≤

Nf < 431

0

≤

N < 215

0

≤

Nr < 511

0

≤

Nf < 511

0

≤

N < 255

0

≤

Nr < 287

0

≤

Nf < 287

0

≤

N < 145

32

36

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA4955 | 2.9-Mbit field memory |

| SAA4955TJ | 2.9-Mbit field memory |

| SAA4956TJ | 2.9-Mbit field memory with noise reduction |

| SAA4960 | Integrated PAL comb filter |

| SAA4963 | Integrated NTSC comb filter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA4955 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:2.9-Mbit field memory |

| SAA4955TJ | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:2.9-Mbit field memory |

| SAA4956TJ | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:2.9-Mbit field memory with noise reduction |

| SAA4960 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Integrated PAL comb filter |

| SAA4963 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Integrated NTSC comb filter |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。