- 您現在的位置:買賣IC網 > PDF目錄376337 > SC14422RVJG (NATIONAL SEMICONDUCTOR CORP) Complete Baseband Processor for DECT Base Stations PDF資料下載

參數資料

| 型號: | SC14422RVJG |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 無繩電話/電話 |

| 英文描述: | Complete Baseband Processor for DECT Base Stations |

| 中文描述: | TELECOM, CORDLESS, BASEBAND CIRCUIT, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁數: | 6/7頁 |

| 文件大小: | 82K |

| 代理商: | SC14422RVJG |

Copyright 1998 National Semiconductor Corp.

6

www.national.com

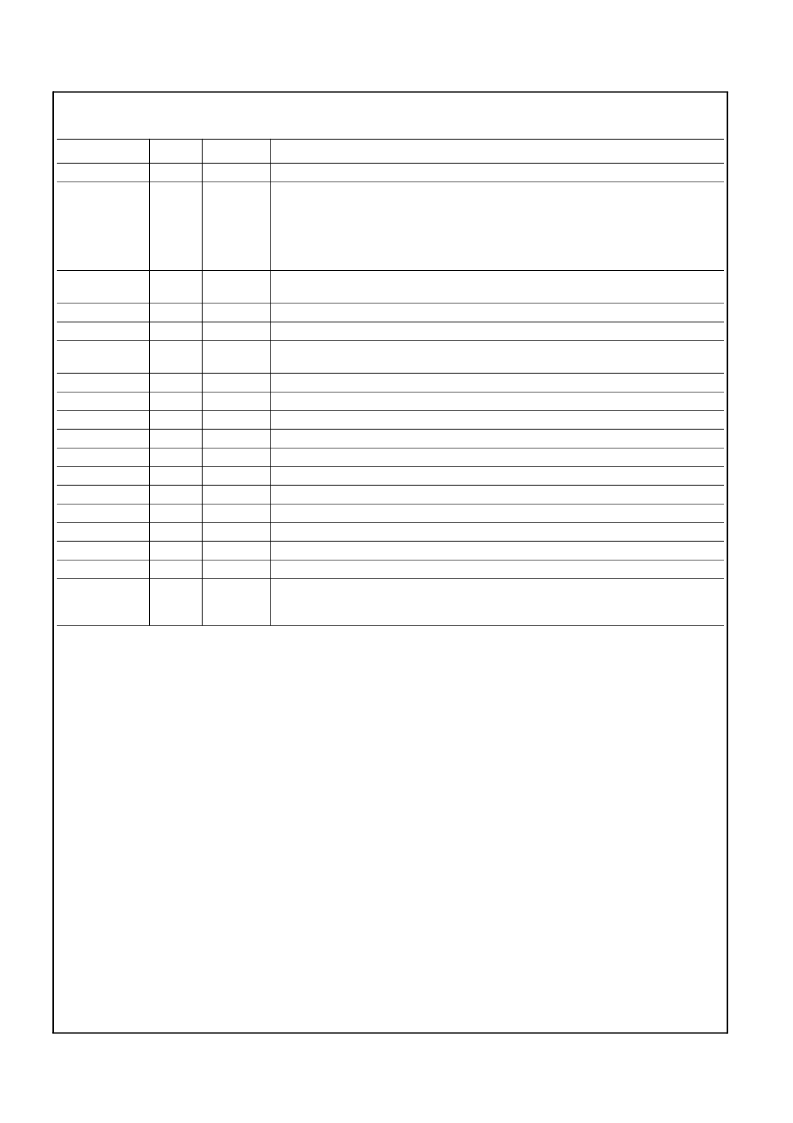

NOTE: All digital outputs can sink/source 2 mA unless otherwise specified. All digital inputs are Schmitt trigger

types. After reset all I/Os are set to input and all pull-up or pull-down resistors are enabled. The p0[0] pull-

up resistor is disabled at start-up.

RSTn

HOLDn

or MI

68

69

1

2

INPUT. Active low Reset.

INPUT/OUTPUT with fixed pull up. Selects HOLD mode. If set to ‘0’, the CR16A

processor will terminate its current instruction and the ADx, WRN, RDN will go TRI-

STATE. In this mode an external CR16A can control the SC14422 completely.

In Emulation mode MI output is automatically selected. Then this pin goes high if

an internal interrupt is asserted. In core mode this pin is a maskable interrupt input

MI to the CR16A core.

OUTPUT. Auxiliary Chip Select not. This signal becomes low if the address range

is within the programmed address range.

OUTPUT. Address bit 3 to 0. In HOLD mode these pins are input.

INPUT/OUTPUT. Data bus bit 7..0

OUTPUT. ROM Chip Select not. Low active if none of the internal peripherals or the

ACSn is addressed.

OUTPUT. Address bit 10. In HOLD mode this pin is input.

OUTPUT. Active low read. In HOLD mode this pin is input.

OUTPUT. Address bit 11. In HOLD mode this pin is input.

OUTPUT. Address bit 9. In HOLD mode this pin is input.

OUTPUT. Address bit 8. In HOLD mode this pin is input.

OUTPUT. Address bit 13. In HOLD mode this pin is input.

OUTPUT. Address bit 14. In HOLD mode this pin is input.

OUTPUT. Address bit 17. In HOLD mode this pin is output.

OUTPUT. Active low write signal. In HOLD mode this pin is input.

OUTPUT. Address bit 16,15 & 12. In HOLD mode these pins are input.

OUTPUT. Address bit 7 to 4. In HOLD mode these pins are input.

OUTPUT. Fixed bit clock output (1.152Mhz). Synchronized to the DECT bit clock.

Will be logic ‘0’ if the DECT Dedicated Instruction Processor (DIP) is frozen.

Will be logic ‘1’ after a hardware reset (RSTN) or software reset (DEBUG_REG[1]).

ACSn

70

5

AD3..0

DAB7..0

RCSn

71-74

82-75

83

1

1

5

AD10

RDn

AD11

AD9

AD8

AD13

AD14

AD17

WRn

AD16,15, 12

AD7-4

CLK1M

84

85

86

87

88

89

90

91

92

1

1

1

1

1

1

1

1

1

1

1

1

93-95

96-99

100

Table 1:

Pin Description)

PIN NAME

NR

TYPE

DESCRIPTION

相關PDF資料 |

PDF描述 |

|---|---|

| SC14422 | Complete Baseband Processor for DECT Base Stations |

| SC14422VJG | Complete Baseband Processor for DECT Base Stations |

| SC14425 | Complete Baseband processor for DECT Base Stations with Caller-id and Handsfree |

| SC14425XVJG | Complete Baseband processor for DECT Base Stations with Caller-id and Handsfree |

| SC14428 | Baseband Processor for FP & PP DECT and WDCT |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SC14422VJG | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Complete Baseband Processor for DECT Base Stations |

| SC14425 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Complete Baseband processor for DECT Base Stations with Caller-id and Handsfree |

| SC14425XVJG | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Complete Baseband processor for DECT Base Stations with Caller-id and Handsfree |

| SC14428 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Baseband Processor for FP & PP DECT and WDCT |

| SC14453VOIPDEVKT | 制造商:DIALOG SEMICONDUCTOR 功能描述:Green VoIP Processor w/ Integrated Audio,Security & Graphics 制造商:Dialog Semiconductor GmbH 功能描述:Green VoIP Processor w/ Integrated Audio,Security & Graphics |

發(fā)布緊急采購,3分鐘左右您將得到回復。