- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376341 > SCM69C432 (Motorola, Inc.) 16K x 64Content Addressable Memory(16K x 64內(nèi)容可尋址存儲器) PDF資料下載

參數(shù)資料

| 型號: | SCM69C432 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 16K x 64Content Addressable Memory(16K x 64內(nèi)容可尋址存儲器) |

| 中文描述: | 16K的x 64Content尋址存儲器(16K的× 64內(nèi)容可尋址存儲器) |

| 文件頁數(shù): | 5/20頁 |

| 文件大?。?/td> | 160K |

| 代理商: | SCM69C432 |

MCM69C432

SCM69C432

5

MOTOROLA FAST SRAM

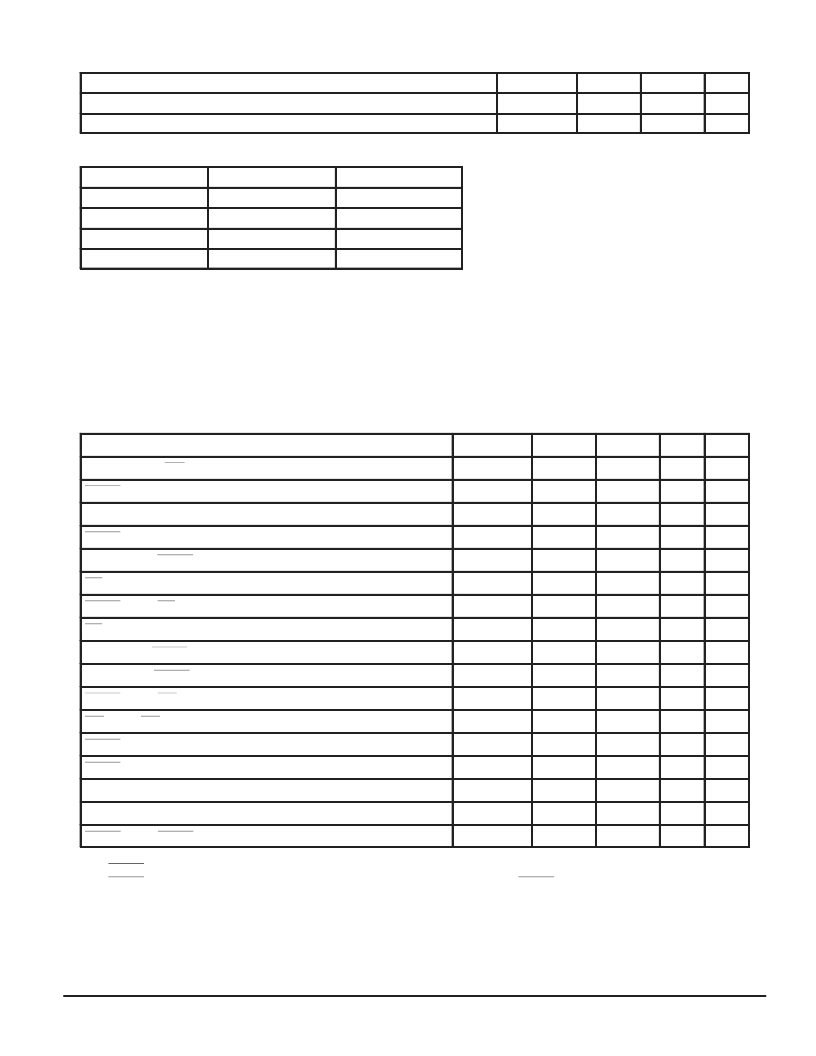

CAPACITANCE

(Periodically Sampled Rather Than 100% Tested)

Parameter

Symbol

Min

Max

Unit

Input Capacitance

Cin

CI/O

—

5

pF

I/O Capacitance

—

8

pF

JUNCTION TO AMBIENT THERMAL CHARACTERISTICS

Board

Air (LFPM)

θ

JA (

°

C/W)

43

1 Layer

0

1 Layer

200

36

4 Layer

0

33

4 Layer

200

29

AC OPERATING CONDITIONS AND CHARACTERISTICS

(VDD = 3.3 V

±

5%, TJ < 120

°

C, Unless Otherwise Noted)

Input Timing Measurement Reference Level

Input Pulse Levels

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Rise/Fall Time

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 V

. . . . . . . . . . . . . . .

0 to 3.0 V

3 ns

Output Timing Reference Level

Output Load

. . . . . . . . . . . . . . . . . .

1.5 V

. . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 1 Unless Otherwise Noted

CONTROL PORT TIMINGS

(Voltages Referenced to VSS = 0 V, Max’s are tKHKH Dependent and Listed Values are for tKHKH = 20 ns)

Parameter

Symbol

Min

Max

Unit

Notes

Address Valid to SEL Low

tAVSL

0

—

ns

DTACK Low to Address Invalid

tDTLAX

0

—

ns

Data Valid to Select Low

tDVSL

0

—

ns

DTACK Low to Data Invalid

tDTLDX

0

—

ns

Output Valid to DTACK Low

tQVDTL

2

—

ns

WE Valid to Select Low

tWVSL

0

—

ns

DTACK Low to WE High

tDTLWH

0

—

ns

WE High to Output Active

tWHQX

2

—

ns

Select Low to DTACK Low

tSLDTL

10

—

ns

1

Select High to DTACK High

tSHDTH

10

—

ns

DTACK Low to IRQ Low

tDTLIL

10

—

ns

IRQ Low to IRQ High

tILIH

20

—

ns

DTACK Low to Select High

tDTLSH

0

—

ns

DTACK High to Select Low

tDTHSL

0

—

ns

Address Valid to Output Valid

tAVQV

—

8

ns

Select High to Output High Impedance

tSHQZ

—

8

ns

RESET Low to RESET High

tRLRH

tKHKH

—

ns

2

NOTE:

1. DTACK is delayed when a write is attempted during certain operations. See Functional Description.

2. RESET must be held low for one clock cycle, except when powering up the SCM69C432. RESET must be held low for 1 second in that case.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCM69C433 | A Flexible Content-Addressable Memory (16K x 64 CAM)(1M內(nèi)容可尋址存儲器) |

| SD1012-03 | Side Door Adapter |

| SD1013-03 | RF MICROWAVE TRANSISTORS 108-152 MHZ APPLICATIONS |

| SD1013-3 | RF & MICROWAVE TRANSISTORS 108-152 MHz APPLICATIONS |

| SD1014-02 | PTSE 8C 8#20 PIN RECP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCM69C433 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16K x 64 CAM |

| SCM69C433TQ15 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16K x 64 CAM |

| SCM69C433TQ15R | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16K x 64 CAM |

| SCM8245ALVV400D | 制造商:Freescale Semiconductor 功能描述:INTEGEATED HOST PROC |

| SCM8245ALZU400D | 制造商:Freescale Semiconductor 功能描述:INTEGRATED HOST PROC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。