- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372130 > SCN2651 (NXP Semiconductors N.V.) Programmable communications interface PCI PDF資料下載

參數(shù)資料

| 型號(hào): | SCN2651 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Programmable communications interface PCI |

| 中文描述: | 可編程通信接口的PCI |

| 文件頁(yè)數(shù): | 8/15頁(yè) |

| 文件大小: | 118K |

| 代理商: | SCN2651 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

Philips Semiconductors

Product specification

SCN2651

Programmable communications interface (PCI)

1994 Apr 27

8

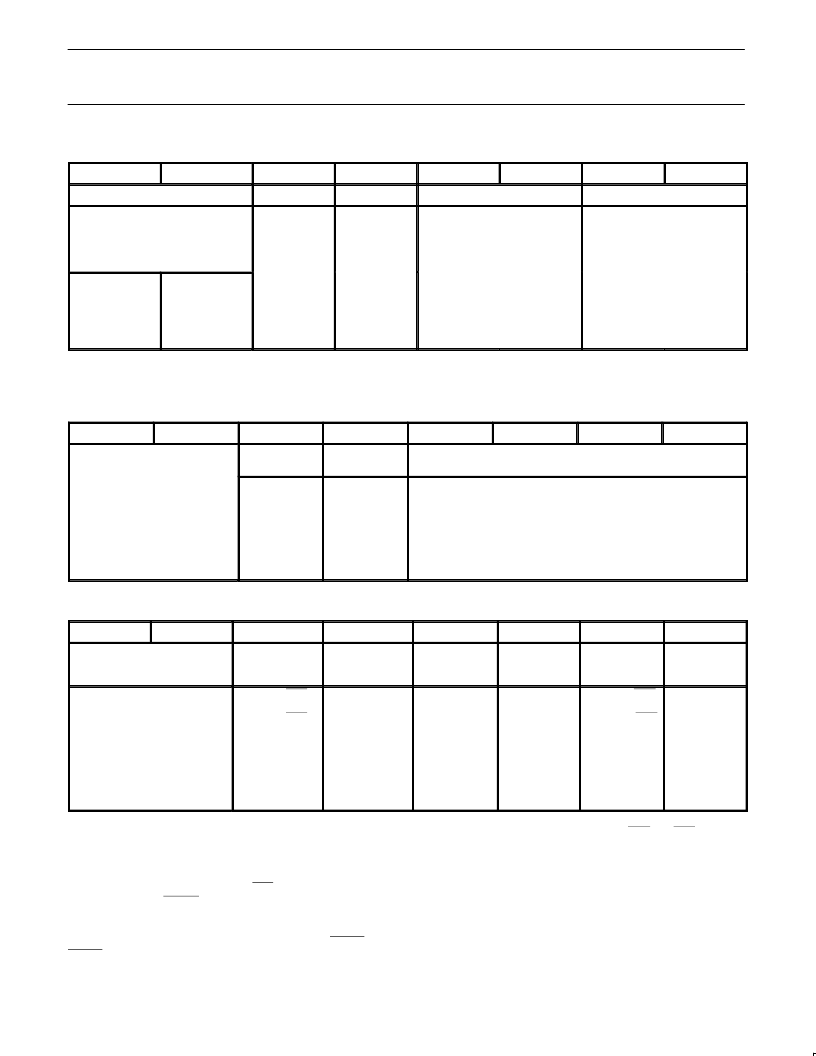

Table 5.

Mode Register 1 (MR1)

MR17

MR16

MR15

MR14

MR13

MR12

MR11

MR10

Parity Type

Parity Control

Character Length

Mode and Baud Rate Factor

Async: Stop bit length

00 = Invalid

01 = 1 Stop bit

10 = 1 1/2 Stop bits

11 = 2 Stop bits

0 = Odd

1 = Even

0 = Disabled

1 = Enabled

00 = 5 Bits

01 = 6 Bits

10 = 7 Bits

11 = 8 Bits

00 = Synchronous 1X rate

01 = Asynchronous 1X rate

10 = Asynchronous 16X rate

11 = Asynchronous 64X rate

Sync:

Number of SYN

char

0 = Double SYN

1 = Single SYN

Sync:

Transparency

control

0 = Normal

1 = Transparent

NOTE:

Baud rate factor in asynchronous applies only if external clock is selected. Factor is 16X if internal clock is selected. Mode must be selected

(MR11, MR10) in any case.

Table 6.

Mode Register 2 (MR2)

MR27

MR26

MR25

MR24

MR23

MR22

MR21

MR20

Transmitter

Clock

Receiver

Clock

Baud Rate Selection

Not used

0 = External

1 = Internal

0= External

1 = Internal

0000 = 50 Baud

0001 = 75

0010 = 110

0011 = 134.5

0100 = 150

0101 = 300

0110 = 600

0111 = 1200

1000 = 1800 Baud

1001 = 2000

1010 = 2400

1011 = 3600

1100 = 4800

1101 = 7200

1110 = 9600

1111 = 19,200

Table 7.

Command Register (CR)

CR7

CR6

CR5

CR4

CR3

CR2

CR1

CR0

Operating Mode

Request

to Send

Reset Error

Receive

Control

(RxEN)

Data Terminal

Ready

Transmit

Control

(TxEN)

00 = Normal operation

01 = Async: automatic

echo mode

Sync: SYN and/or DLE

stripping mode

10 = Local Loopback

11 = Remote Loopback

0 = Force RTS

output high

1 = Force RTS

output low

0 = Normal

1 = Reset

error flag

in status reg

(FE, OE,

PE/DLE

DETECT)

Async:

Force Break

0 = Normal

1 = Force

break

Sync

Send DLE

0 = Normal

1 = Send DLE

0 = Disable

1 = Enable

0 = Force DTR

output high

1 = Force DTR

output low

0 = Disable

1 = Enable

Command Register (CR)

Table 7 illustrates the command register. Bits CR0 (TxEN) and CR2

(RxEN) enable or disable the transmitter and receiver respectively.

A 0 to 1 transition of CR2 forces start bit search (async mode) or

hunt mode (sync mode) on the second RxC rising edge. Disabling

the receiver causes RxRDY to go high (inactive). If the transmitter

is disabled, it will complete the transmission of the character in the

transmit shift register (if any) prior to terminating operation. The TxD

output will then remain in the marking state (high) while TxRDY and

TxEMT will go high (inactive). If the receiver is disabled, it will

terminate operation immediately. Any character being assembled

will be neglected.

Bits CR1 (DTR) and CR5 (RTS) control the DTR and RTS outputs.

Data at the outputs is the logical complement of the register data.

In asynchronous mode, setting CR3 will force and hold the TxD

output low (spacing condition) at the end of the current transmitted

character. Normal operation resumes when CR3 is cleared. The

TxD line will go high for at least one bit time before beginning

transmission of the next character in the transmit data holding

register. In synchronous mode, setting CR3 causes the

transmission of the DLE register contents prior to sending the

character in the transmit data holding register. CR3 should be reset

in response to the next TxRDY.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCN2651CC1N28 | Programmable communications interface PCI |

| SCN2652 | Multi-protocol communications controller MPCC |

| SCN2652AC2A44 | NT Series Toggle Switch, 1 pole, 3 position, Solder terminal, Locking Lever |

| SCN2652AC2N40 | Multi-protocol communications controller MPCC |

| SCN68652 | Multi-protocol communications controller MPCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCN2651C1N28 | 制造商:North American Philips Discrete Products Div 功能描述:1 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, PDIP28 |

| SCN2651CC1I28 | 制造商:NXP Semiconductors 功能描述:IC,COMMUNICATIONS INTERFACE,MOS,DIP,28PIN,CERAMIC |

| SCN2651CC1N28 | 制造商:NXP Semiconductors 功能描述:COMMUNICATIONS INTERFACE, 28 Pin, Plastic, DIP |

| SCN2652 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multi-protocol communications controller MPCC |

| SCN2652AC1I40 | 制造商:North American Philips Discrete Products Div 功能描述:COMMUNICATIONS INTERFACE, 40 Pin, Ceramic, DIP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。