- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄2017 > SN75LVDS83CZQLR (Texas Instruments)IC FLATLINK TX 10-85MHZ 56BGA PDF資料下載

參數(shù)資料

| 型號: | SN75LVDS83CZQLR |

| 廠商: | Texas Instruments |

| 文件頁數(shù): | 9/27頁 |

| 文件大小: | 0K |

| 描述: | IC FLATLINK TX 10-85MHZ 56BGA |

| 標準包裝: | 1,000 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

SN75LVDS83C

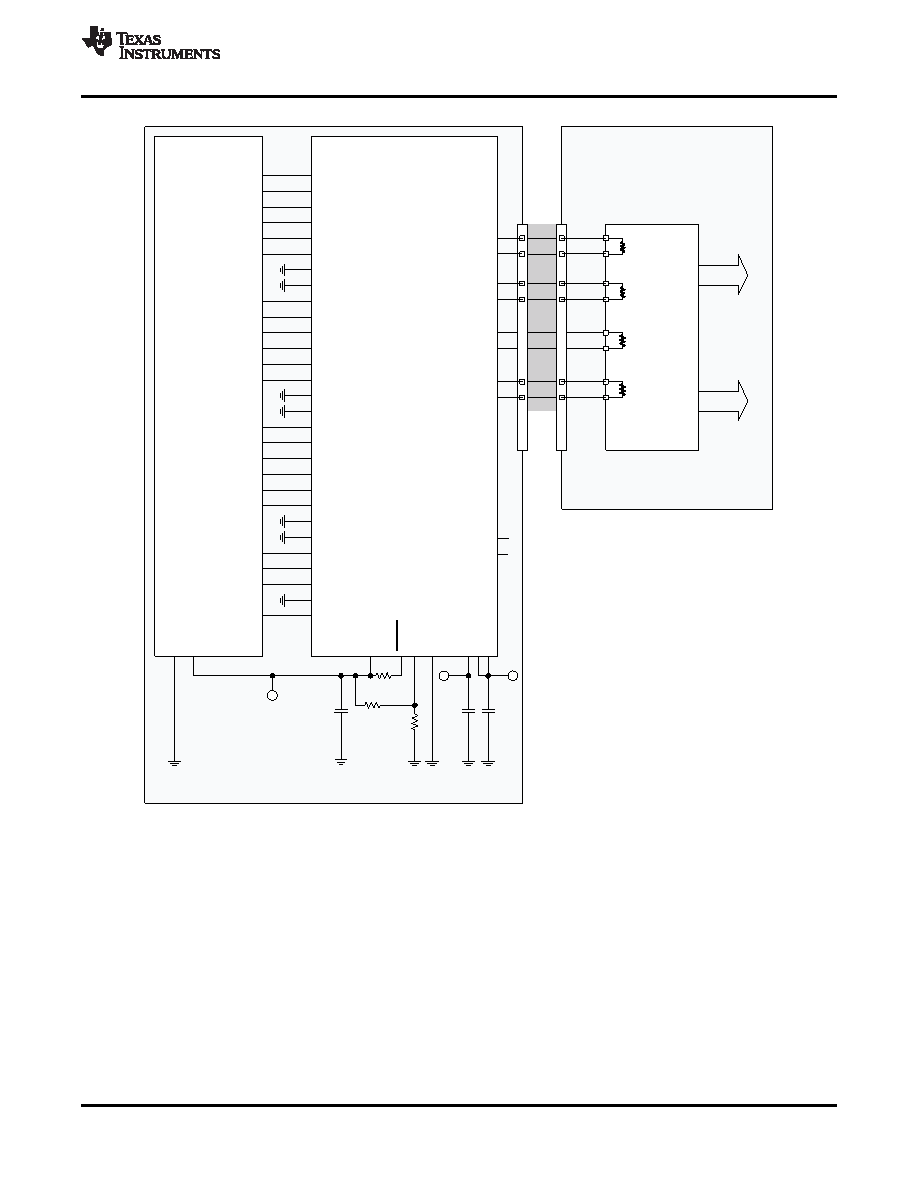

24-bpp GPU

R2

R3

R4

R5

R6

R7(MSB)

G2

G3

G4

G5

G6

G7(MSB)

B2

B3

B4

B5

B6

B7(MSB)

HSYNC

VSYNC

ENABLE

RSVD

CLK

D0

D1

D2

D3

D4

D6

D27

D5

D7

D8

D9

D12

D13

D14

D10

D11

D15

D18

D19

D20

D21

D22

D16

D17

D24

D25

D26

D23

CLKIN

Y0M

Y0P

Y1M

Y1P

Y2M

Y2P

CLKOUTM

CLKOUTP

Y3M

Y3P

FPC

Cable

V

D

G

P

U

IO

1.8V or 2.5V

or 3.3V

G

N

D

IO

V

C

L

K

S

E

L

Rpullup

Rpulldown

(See Note C)

(See Note A)

V

C

LV

D

S

V

C

P

L

V

C

G

N

D

3.3V

C2

C1

C3

3.3V

100

LVDS

timing

Controller

(6-bpc, 18-bpp)

l

t

100

to column

driver

to row driver

Main Board

18-bpp LCD Display

SH

TDN

4.8k

Panel

connector

Main

board

connector

R0 and R1: NC

(See Note B)

B0 and B1: NC

(See Note B)

G0 and G1: NC

(See Note B)

B0 and B1: NC

(See Note B)

SLLSE66A

– OCTOBER 2010 – REVISED SEPTEMBER 2011

Note A. Leave output Y3 NC.

Note B. R0, R1, G0, G1, B0, B1: For improved image quality, the GPU should dither the 24-bit output pixel down

to18-bit per pixel.

NoteC.Rpullup: install only to use rising edge triggered clocking.

Rpulldown: install only to use falling edge triggered clocking.

C1: decoupling cap for the VDDIO supply; install at least 1x0.01

F.

C2: decoupling cap for the VDD supply; install at least 1x0.1

F and 1x0.01F.

C3: decoupling cap for the VDDPLL and VDDLVDS supply; install at least 1x0.1

F and 1x0.01F.

Figure 14. 24-Bit Color Host to 18-Bit Color LCD Panel Display Application

Copyright

2010–2011, Texas Instruments Incorporated

17

Product Folder Link(s): SN75LVDS83C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SP3220EUEA-L/TR | IC DVR/RCVR RS232 ESD 16SSOP |

| SP3226EEA-L | IC TXRX RS232 ESD SD 16SSOP |

| SP3244EER1-L | IC TXRX RS232 32QFN |

| SP336EEY-L/TR | IC TXRX RS232/485 PROG 28TSSOP |

| SP491ES-L | IC TXRX RS485 FULL DUPLEX 14PDIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN75LVDS83DGG | 功能描述:總線發(fā)射器 Flatlink RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:135 Mpps 接口: 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSSOP-56 封裝:Reel |

| SN75LVDS83DGG | 制造商:Texas Instruments 功能描述:IC FLATLINK(TM) XMITTER 56-TSSOP 制造商:Texas Instruments 功能描述:IC, FLATLINK(TM) XMITTER 56-TSSOP 制造商:Texas Instruments 功能描述:IC, FLATLINK(TM) XMITTER 56-TSSOP; MSL:MSL 2 - 1 year; SVHC:No SVHC (19-Dec-2012); Base Number:75; Device Type:LVDS; No. of Pins:56; Operating Temperature Max:70C; Operating Temperature Min:0C; Operating Temperature Range:0C to ;RoHS Compliant: Yes |

| SN75LVDS83DGG | 制造商:Texas Instruments 功能描述:SEMICONDUCTOR |

| SN75LVDS83DGGG4 | 功能描述:總線發(fā)射器 Flatlink RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:135 Mpps 接口: 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSSOP-56 封裝:Reel |

| SN75LVDS83DGG-P | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。