- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98143 > ST10F269DIETR (STMICROELECTRONICS) 16-BIT, FLASH, 32 MHz, MICROCONTROLLER, UUC PDF資料下載

參數(shù)資料

| 型號(hào): | ST10F269DIETR |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, FLASH, 32 MHz, MICROCONTROLLER, UUC |

| 封裝: | DIE |

| 文件頁(yè)數(shù): | 103/161頁(yè) |

| 文件大?。?/td> | 1595K |

| 代理商: | ST10F269DIETR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)當(dāng)前第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)

ST10F269-T3

46/160

Hardware traps are exceptions or error conditions

that arise during run-time. They cause immediate

non-maskable

system

reaction

similar

to

a

standard

interrupt

service

(branching

to

a

dedicated vector table location).

The occurrence of a hardware trap is additionally

signified by an individual bit in the trap flag

register (TFR). Except when another higher

prioritized trap service is in progress, a hardware

trap will interrupt any other program execution.

Hardware trap services cannot not be interrupted

by standard interrupt or by PEC interrupts.

8.3 - Interrupt Control Registers

All interrupt control registers are

identically

organized. The lower 8 bits of an interrupt control

register contain the complete interrupt status

information of the associated source, which is

required during one round of prioritization, the

upper 8 bits of the respective register are

reserved. All interrupt control registers are bit

addressable and all bits can be read or written via

software.

This

allows

each

interrupt

source

to

be

programmed or modified with just one instruction.

When

accessing

interrupt

control

registers

through instructions which operate on Word data

types, their upper 8 bits (15...8) will return zeros,

when read, and will discard written data.

The layout of the Interrupt Control registers shown

below applies to each xxIC register, where xx

stands for the mnemonic for the respective

source.

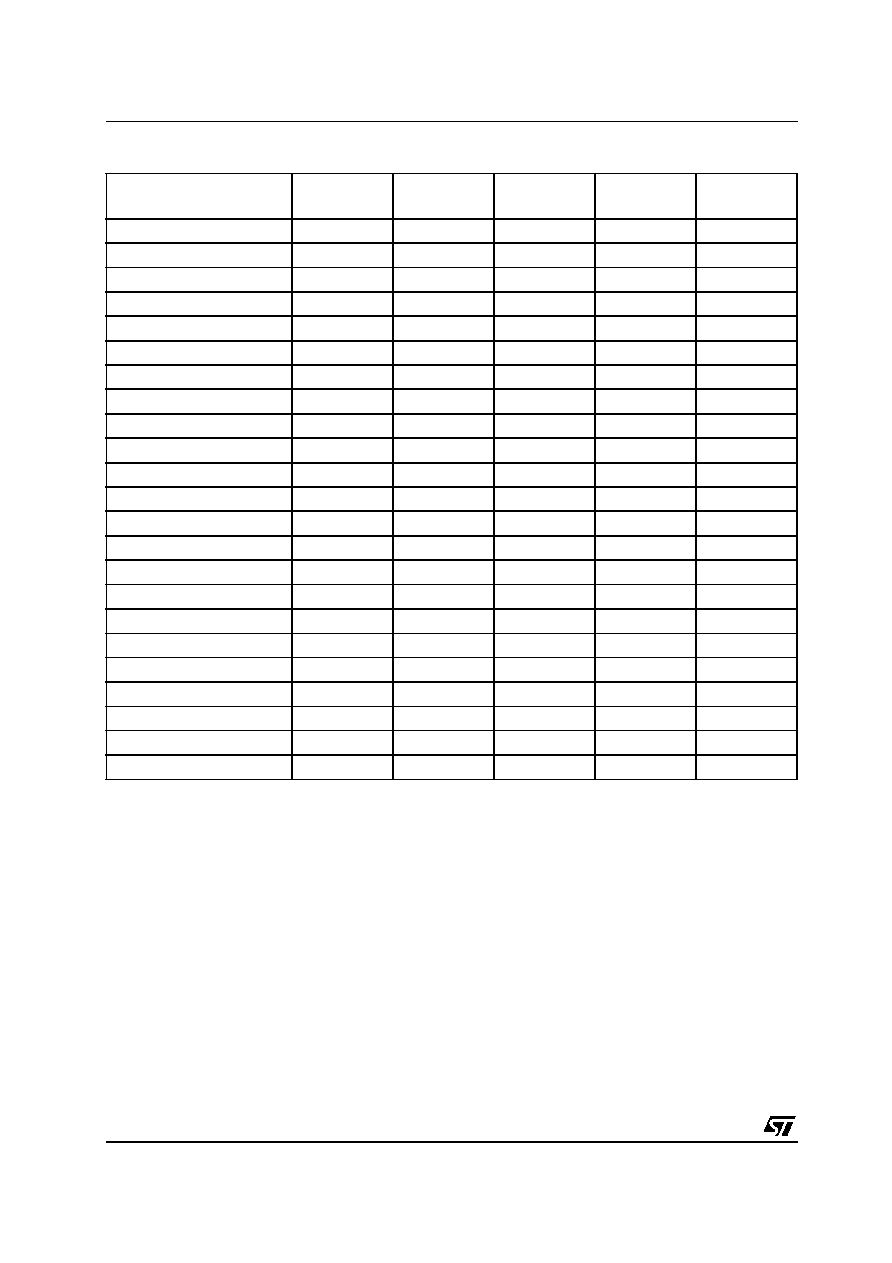

CAPCOM Timer 1

T1IR

T1IE

T1INT

00’0084h

21h

CAPCOM Timer 7

T7IR

T7IE

T7INT

00’00F4h

3Dh

CAPCOM Timer 8

T8IR

T8IE

T8INT

00’00F8h

3Eh

GPT1 Timer 2

T2IR

T2IE

T2INT

00’0088h

22h

GPT1 Timer 3

T3IR

T3IE

T3INT

00’008Ch

23h

GPT1 Timer 4

T4IR

T4IE

T4INT

00’0090h

24h

GPT2 Timer 5

T5IR

T5IE

T5INT

00’0094h

25h

GPT2 Timer 6

T6IR

T6IE

T6INT

00’0098h

26h

GPT2 CAPREL Register

CRIR

CRIE

CRINT

00’009Ch

27h

A/D Conversion Complete

ADCIR

ADCIE

ADCINT

00’00A0h

28h

A/D Overrun Error

ADEIR

ADEIE

ADEINT

00’00A4h

29h

ASC0 Transmit

S0TIR

S0TIE

S0TINT

00’00A8h

2Ah

ASC0 Transmit Buffer

S0TBIR

S0TBIE

S0TBINT

00’011Ch

47h

ASC0 Receive

S0RIR

S0RIE

S0RINT

00’00ACh

2Bh

ASC0 Error

S0EIR

S0EIE

S0EINT

00’00B0h

2Ch

SSC Transmit

SCTIR

SCTIE

SCTINT

00’00B4h

2Dh

SSC Receive

SCRIR

SCRIE

SCRINT

00’00B8h

2Eh

SSC Error

SCEIR

SCEIE

SCEINT

00’00BCh

2Fh

PWM Channel 0...3

PWMIR

PWMIE

PWMINT

00’00FCh

3Fh

CAN1 Interface

XP0IR

XP0IE

XP0INT

00’0100h

40h

CAN2 Interface

XP1IR

XP1IE

XP1INT

00’0104h

41h

FLASH Ready / Busy

XP2IR

XP2IE

XP2INT

00’0108h

42h

PLL Unlock/OWD

XP3IR

XP3IE

XP3INT

00’010Ch

43h

Table 7 : Interrupt Sources (continued)

Source of Interrupt or PEC

Service Request

Request

Flag

Enable

Flag

Interrupt

Vector

Location

Trap

Number

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST10F269Z2Q3 | 16-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP144 |

| ST10F269Z2Q6 | 16-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP144 |

| ST10F276Z5Q3 | 16-BIT, MROM, 64 MHz, RISC MICROCONTROLLER, PQFP144 |

| ST10F296TR | 16-BIT, FLASH, 64 MHz, MICROCONTROLLER, PBGA208 |

| ST10R172LT6 | 16-BIT, 50 MHz, MICROCONTROLLER, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST10F269-DP | 功能描述:16位微控制器 - MCU 16-bit MCU MAC 256 Kbyte Flash RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| ST10F269-DPB | 功能描述:16位微控制器 - MCU 16-bit MCU MAC 256 Kbyte Flash RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| ST10F269-DPR | 功能描述:16位微控制器 - MCU 16Bit MCU 256K BYTE FLASH,12K BYTE RAM RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| ST10F269DT3 | 功能描述:16位微控制器 - MCU 16Bit MCU 256K BYTE FLASH,12K BYTE RAM RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| ST10F269DTR3 | 功能描述:16位微控制器 - MCU 16-bit MCU MAC unit 256 Kbyte Flash RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。