- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98145 > ST72F60K2DIE1 (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, UUC PDF資料下載

參數(shù)資料

| 型號: | ST72F60K2DIE1 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, UUC |

| 文件頁數(shù): | 41/121頁 |

| 文件大?。?/td> | 2515K |

| 代理商: | ST72F60K2DIE1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁

ST7260

26/117

8 POWER SAVING MODES

8.1 Introduction

To give a large measure of flexibility to the applica-

tion in terms of power consumption, two main pow-

er saving modes are implemented in the ST7.

After a RESET, the normal operating mode is se-

lected by default (RUN mode). This mode drives

the device (CPU and embedded peripherals) by

means of a master clock which is based on the

main oscillator frequency divided by 3 (fCPU).

From Run mode, the different power saving

modes may be selected by setting the relevant

register bits or by calling the specific ST7 software

instruction whose action depends on the oscillator

status.

8.2 HALT Mode

The MCU consumes the least amount of power in

HALT mode. The HALT mode is entered by exe-

cuting the HALT instruction. The internal oscillator

is then turned off, causing all internal processing to

be stopped, including the operation of the on-chip

peripherals.

When entering HALT mode, the I bit in the Condi-

tion Code Register is cleared. Thus, all external in-

terrupts (ITi or USB end suspend mode) are al-

lowed and if an interrupt occurs, the CPU clock be-

comes active.

The MCU can exit HALT mode on reception of ei-

ther an external interrupt on ITi, an end suspend

mode interrupt coming from USB peripheral, or a

reset. The oscillator is then turned on and a stabi-

lization time is provided before releasing CPU op-

eration. The stabilization time is 4096 CPU clock

cycles.

After the start up delay, the CPU continues opera-

tion by servicing the interrupt which wakes it up or

by fetching the reset vector if a reset wakes it up.

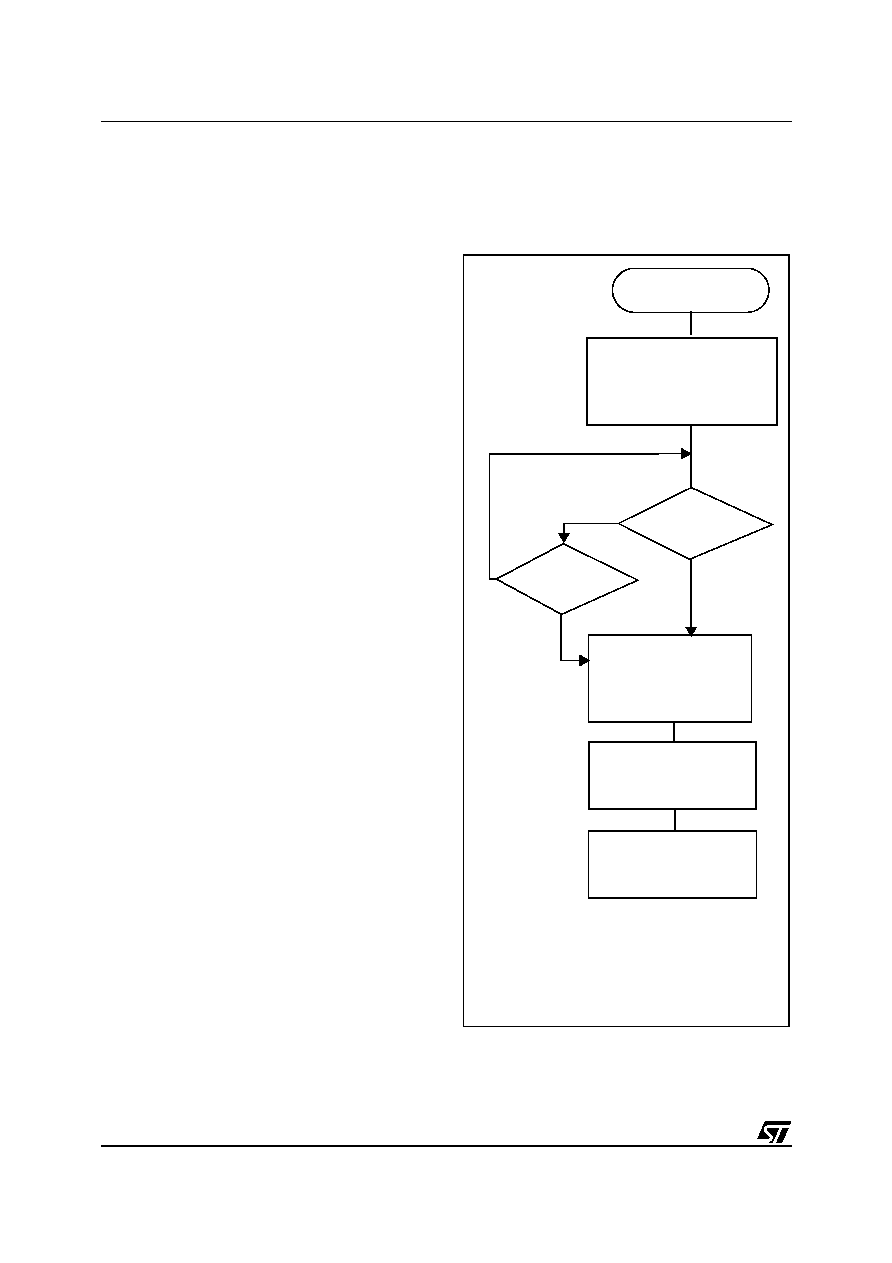

Figure 17. HALT Mode Flow Chart

N

EXTERNAL

INTERRUPT*

RESET

HALT INSTRUCTION

4096 CPU CLOCK

FETCH RESET VECTOR

OR SERVICE INTERRUPT

CYCLES DELAY

CPU CLOCK

OSCILLATOR

PERIPH. CLOCK

I-BIT

ON

SET

ON

CPU CLOCK

OSCILLATOR

PERIPH. CLOCK

I-BIT

OFF

CLEARED

OFF

Y

Note: Before servicing an interrupt, the CC register is

pushed on the stack. The I-Bit is set during the inter-

rupt routine and cleared when the CC register is

popped.

相關PDF資料 |

PDF描述 |

|---|---|

| ST72F60K2DIE6 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, UUC |

| ST72F651AR6T1 | 8-BIT, FLASH, MICROCONTROLLER, PQFP64 |

| ST72P60E2M1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO24 |

| ST7260E2M1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO24 |

| ST72T141K2M6XXX | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO34 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ST72F60K2U1TR | 功能描述:8位微控制器 -MCU ST7262 Lo Spd USB 8B MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風格:SMD/SMT |

| ST72F621J4B1 | 功能描述:8位微控制器 -MCU Flash 16K USB/SPI/SC RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風格:SMD/SMT |

| ST72F621J4D0 | 功能描述:8位微控制器 -MCU Flash 16K USB/SPI/SC RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風格:SMD/SMT |

| ST72F621J4T1 | 功能描述:8位微控制器 -MCU ST7262 Lo Spd USB 8B MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風格:SMD/SMT |

| ST72F621K4B1 | 功能描述:8位微控制器 -MCU Flash 16K USB/SPI/SC RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復。