- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371182 > TDA8757 (NXP Semiconductors N.V.) Triple 8-bit ADC 170 Msps PDF資料下載

參數(shù)資料

| 型號(hào): | TDA8757 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Triple 8-bit ADC 170 Msps |

| 中文描述: | 三路8位ADC為170 MSPS |

| 文件頁(yè)數(shù): | 16/37頁(yè) |

| 文件大?。?/td> | 895K |

| 代理商: | TDA8757 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)

Philips Semiconductors

TDA8757

Triple 8-bit ADC 170 Msps

Preliminary data

Rev. 07 — 28 February 2002

16 of 37

9397 750 09457

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

It is possible to control the phase of the ADC clock (CKADC) through the serial

interface with the included digital phase-shift controller. The phase register (5 bits)

enables the phase to shift by steps of 11.25

°

.

The CKREF signal is re-synchronized by the synchro-block on the CKADC clock. The

new reference is available on pin CKREFO. This synchronization may be done with

the CKREF signal directly, or with the output of the divider in the PLL (see

Figure 3

).

The selection is done via the serial interface by setting bit ‘Ckrs’ in the phase register

(Ckrs = 1 when the CKREF signal is used). The polarity of the signal on pin CKREFO

is controlled through the serial interface by setting bit ‘Ckrp’ in register DEMUX

(positive polarity if Ckrp = 0). The width of this signal is fixed to 8 clock cycles.

The PLL also provides a CKDATA clock. This clock is synchronized on the data

outputs whatever the output mode.

It is possible to delay the CKDATA clock with a constant time (

τ = 3

ns, compared to

the outputs) by setting bit ‘Ckdd’ to logic 1 in register DEMUX. It is also possible to

reverse the CKDATA clock, referenced to the outputs, by setting bit ‘Ckdp’ in

register DEMUX.

The maximum capacitive load for each clock output is 10 pF, and pin OE switches the

output status between active and high impedance (OE = HIGH).

If an external clock is used, it has to be connected to pin CKEXT. Bit ‘Ckext’ and

bit ‘Ckrs’ in the phase register have to be set at logic 1, and it is also important to

disconnect the internal PLL by using the following settings:

Set bit ‘Do’ in the control register to logic 1.

Set bits ‘Vco1’ and ‘Vco0’ in register VCO to logic 0.

There is a delay between the input signal on pin CKREF and the corresponding

output on pin CKREFO; see

Figure 8

. This delay is t

CKREFO

:

t

CKREFO

= either t

CKAO

(if clock phase >01000) or t

CKAO

+ T

CLK(pixel)

(if phase <01000)

t

CKAO

= t

CLK(buffer)

+ t

phase selector

t

CLK(buffer)

= tbf and t

phase selector

=

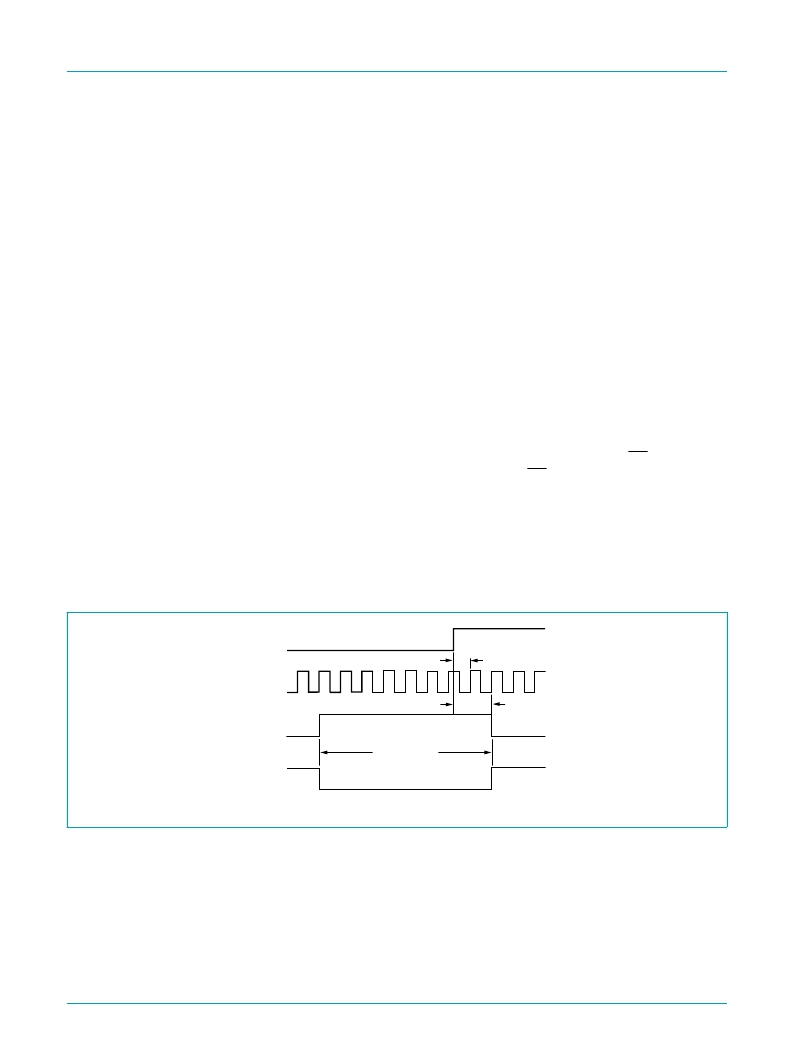

Fig 8.

Timing diagram; CKREFO; Dmx = 0.

CKREF

CKADC

CKREFO

Ckrp = 0

CKREFO

Ckrp = 1

8 clock periods

FCE699

tCKAO

tCKREFO

phase

2

---------------

T

CLK pixel

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TDA8757HL | Triple 8-bit ADC 170 Msps |

| TDA8780M | True logarithmic amplifier |

| TDA8798HL | Dual 8-bit, 100 Msps A/D converter with DPGA |

| TDA8842-N2 | I2C-bus controlled PAL/NTSC/SECAM TV processors |

| TDA8840-N2 | I2C-bus controlled PAL/NTSC/SECAM TV processors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TDA8757HL | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Triple 8-bit ADC 170 Msps |

| TDA8758 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:YC 8-bit low-power analog-to-digital video interface |

| TDA8758G | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:YC 8-bit low-power analog-to-digital video interface |

| TDA8759HV/8/C1 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 3X8-BITS VIDEO ADC 110MSPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TDA8759HV/8/C1,551 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 3X8-BITS VIDEO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。