- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98219 > THS1207IDAG4 (TEXAS INSTRUMENTS INC) 4-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 PDF資料下載

參數(shù)資料

| 型號(hào): | THS1207IDAG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 4-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| 封裝: | GREEN, PLASTIC, TSSOP-32 |

| 文件頁數(shù): | 8/32頁 |

| 文件大小: | 317K |

| 代理商: | THS1207IDAG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

THS1207

SLAS284A – AUGUST 2000 – REVISED DECEMBER 2002

www.ti.com

16

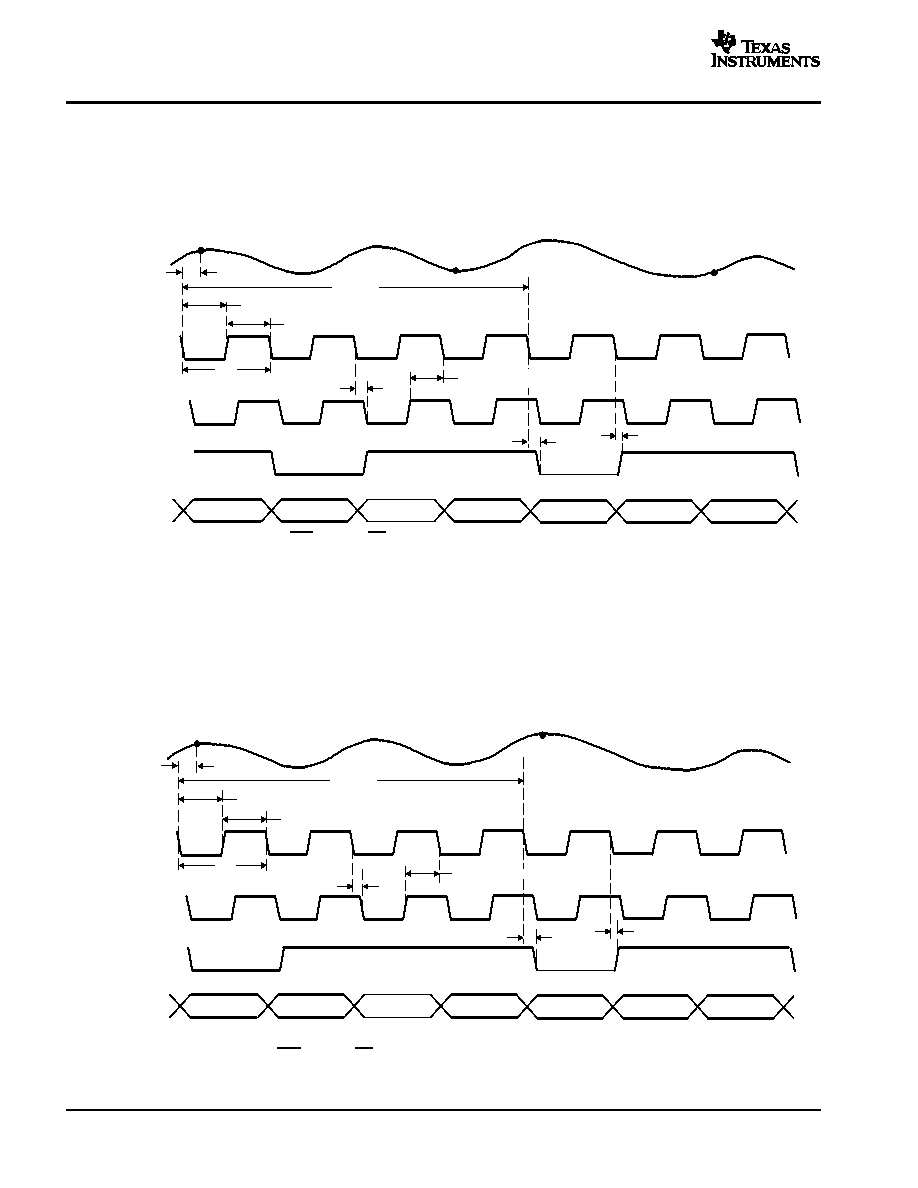

Figure 28 shows the conversion timing when 3 analog input channels are selected. The maximum throughput

rate per channel is 2 MSPS in this mode. The data flow in the bottom of the figure shows in which order the

converted data is available to the databus. The signal SYNC is always active low if data of channel one is

available to the databus. The data of channel one is followed by the data of channel two and data of channel

three before channel one is again available to the data bus and SYNC is active low.

Sample N

Channel 1, 2, 3

Sample N+1

Channel 1, 2, 3

Sample N+2

Channel 1, 2, 3

Data N–1

Channel 3

Data N

Channel 1

Data N

Channel 2

Data N

Channel 3

Data N–2

Channel 3

Data N–1

Channel 1

Data N–1

Channel 2

AIN

CONV_CLK

READ

READ is the logical combination from CS0, CS1 and RD

SYNC

td(A)

td(pipe)

tw(CONV_CLKH)

tw(CONV_CLKL)

tc

tsu(CONV_CLKL-READL)

tsu(READH-CONV_CLKL)

td(CONV_CLKL-SYNCL)

td(CONV_CLKL-SYNCH)

Figure 28. Conversion Timing in 3-Channel Operation

Figure 29 shows the timing of the conversion mode where 4 analog input channels are selected. The maximum

throughput rate per channel is 1.5 MSPS in this mode. The data flow in the bottom of the figure shows in which

order the converted data is available to the databus. The signal SYNC is active low when data of channel one

is available to the databus. The data of channel one is followed by the data of channel two, data of channel three

and data of channel 4 before channel one is again available to the data bus and SYNC is active low.

Sample N

Channel 1, 2, 3, 4

Sample N+1

Channel 1, 2, 3, 4

Data N–1

Channel 4

Data N

Channel 1

Data N

Channel 2

Data N

Channel 3

Data N–1

Channel 1

Data N–1

Channel 2

Data N–1

Channel 3

AIN

CONV_CLK

READ

READ is the logical combination from CS0, CS1 and RD

SYNC

td(A)

td(pipe)

tw(CONV_CLKH)

tw(CONV_CLKL)

tc

tsu(CONV_CLKL-READL)

tsu(READH-CONV_CLKL)

tsu(CONV_CLKL-SYNCH)

tsu(CONV_CLKL-SYNCL)

Figure 29. Timing of Continuous Conversion Mode (4-channel operation)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| THS1207CDAG4 | 4-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1209CDAR | 2-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1209IDAR | 2-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1209IDA | 2-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1209CDA | 2-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS12082 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:12-BIT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTERS |

| THS12082CDA | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12bit 8 MSPS ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS12082CDAG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12 Bit 8 MSPS Dual Ch RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS12082CDAR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12 Bit 8 MSPS Dual Ch RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS12082CDARG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12 Bit 8 MSPS Dual Ch RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。