- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98229 > THS8133BCPHPG4 (TEXAS INSTRUMENTS INC) PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 PDF資料下載

參數(shù)資料

| 型號: | THS8133BCPHPG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| 封裝: | PLASTIC, HTQFP-48 |

| 文件頁數(shù): | 23/25頁 |

| 文件大小: | 549K |

| 代理商: | THS8133BCPHPG4 |

THS8133, THS8133A, THS8133B

TRIPLE 10BIT, 80 MSPS VIDEO D/A CONVERTER

WITH TRILEVEL SYNC GENERATION

SLVS204C APRIL 1999 REVISED SEPTEMBER 2000

7

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

programming example (continued)

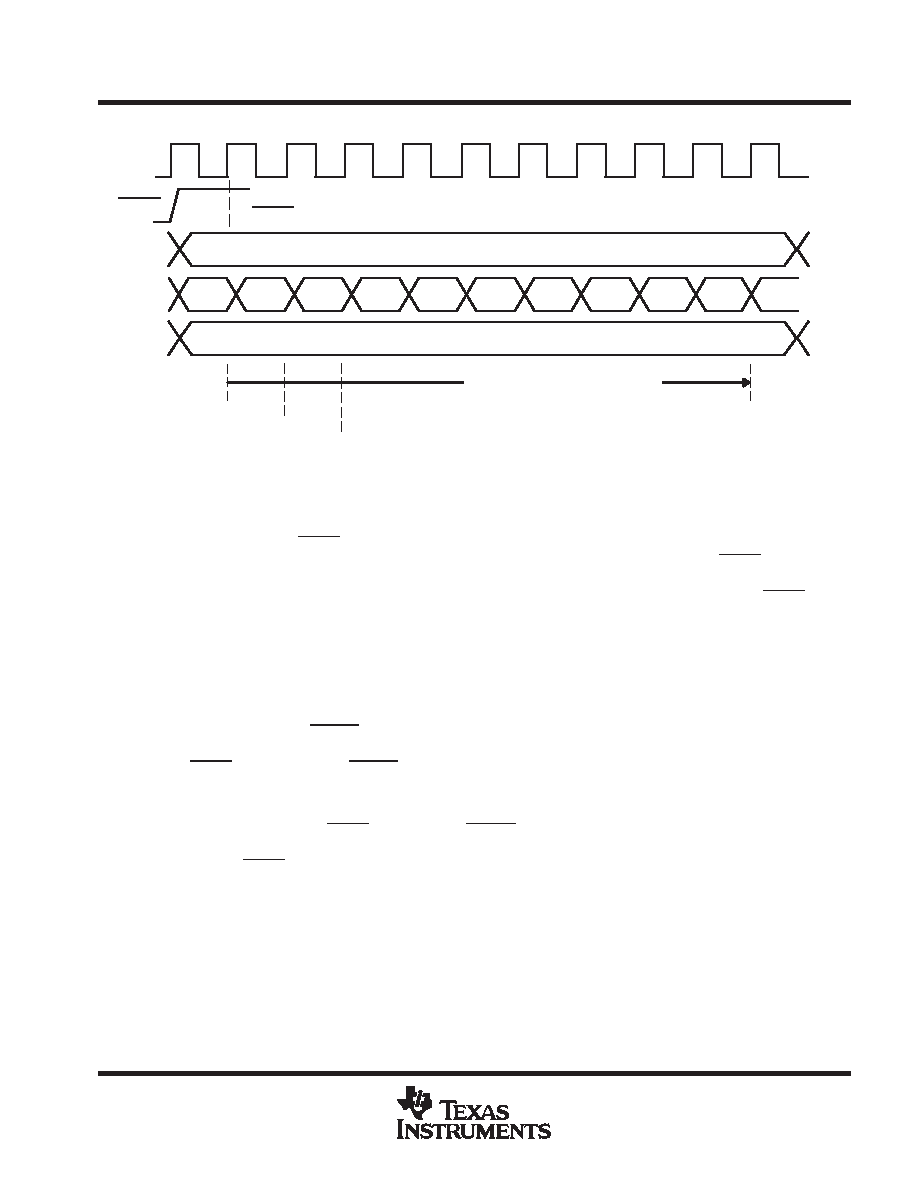

First registered sample on GYr[90] after L-

>H

on BLANK is interpreted as Pb[90]

T0

T1

T2

T3

T4

T5

T6

T7

T8

Pb(0)

Y(0)

Pr(0)

Y(2)

Pb(4)

Y(4)

Pr(4)

Y(6)

Pb(8)

RPr[90]

ARPr, AGY,

ABPb output

corresponding

to Pr(0),

Y(0), Pb(0)

data path latency = 9 CLK cycles

Pb(0)

registered

T9

Y(8)

GY[90]

BPb[90]

BLANK

Y(0)

registered

Pr(8)

T10

Pr(0)

registered

Figure 5. Input Format and Latency YPbPr 4:2:2 1

×10 Bit Mode

sync generation

Additional control inputs SYNC and SYNC_T enable the superposition of an additional current onto the AGY

channel or on all three channels, depending on the setting of INS3_INT. By combining the SYNC and SYNC_T

control inputs, either bi-level negative going pulses or tri-level pulses can be generated. Depending on the timing

controls for these signals, both horizontal and vertical sync signals can be generated. Assertion of SYNC (active

low) will identify the sync period, while assertion of SYNC_T (active high) within this period will identify the

positive excursion of a tri-level sync.

Refer to the application information section for practical examples on the use of these control inputs for sync

generation.

blanking generation

An additional control input BLANK is provided that will fix the output amplitude on all channels to the blanking

level, irrespective of the value on the data input ports. However, sync generation has precedence over blanking;

that is, if SYNC is low, the level of BLANK is don’t care. The absolute amplitude of the blanking level with respect

to active video is determined by the GBR or YPbPr operation mode of the device. Refer to the application

information section for practical examples on the use of this control input for blank generation.

Figure 6 shows how to control SYNC, SYNC_T, and BLANK signals to generate tri-level sync levels and blanking

at the DAC output. A bi-level (negative) sync is generated similarly by avoiding the positive transition on

SYNC_T during SYNC low.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| THS8133CPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8134BCPHP | PARALLEL, 8 BITS INPUT LOADING, 0.005 us SETTLING TIME, 8-BIT DAC, PQFP48 |

| THS8134CPHP | PARALLEL, 8 BITS INPUT LOADING, 0.005 us SETTLING TIME, 8-BIT DAC, PQFP48 |

| THS8134ACPHP | PARALLEL, 8 BITS INPUT LOADING, 0.005 us SETTLING TIME, 8-BIT DAC, PQFP48 |

| THS8135-240IPHP | PARALLEL, WORD INPUT LOADING, 10-BIT DAC, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS8133BEVM | 制造商:Texas Instruments 功能描述:THS8133B TRIPLE 10BIT 80MSPS VID DAC EVM - Bulk |

| THS8133CPHP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION |

| THS8133TQFP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION |

| THS8134 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 8-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION |

| THS8134A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 8-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。