- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383953 > TLC32040C (Texas Instruments, Inc.) ANALOG INTERFACE CIRCUITS PDF資料下載

參數(shù)資料

| 型號: | TLC32040C |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ANALOG INTERFACE CIRCUITS |

| 中文描述: | 模擬接口電路 |

| 文件頁數(shù): | 3/33頁 |

| 文件大小: | 453K |

| 代理商: | TLC32040C |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

TLC32040C, TLC32040I, TLC32041C, TLC32041I

ANALOG INTERFACE CIRCUITS

SLAS014E – SEPTEMBER 1987 – REVISED MAY 1995

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

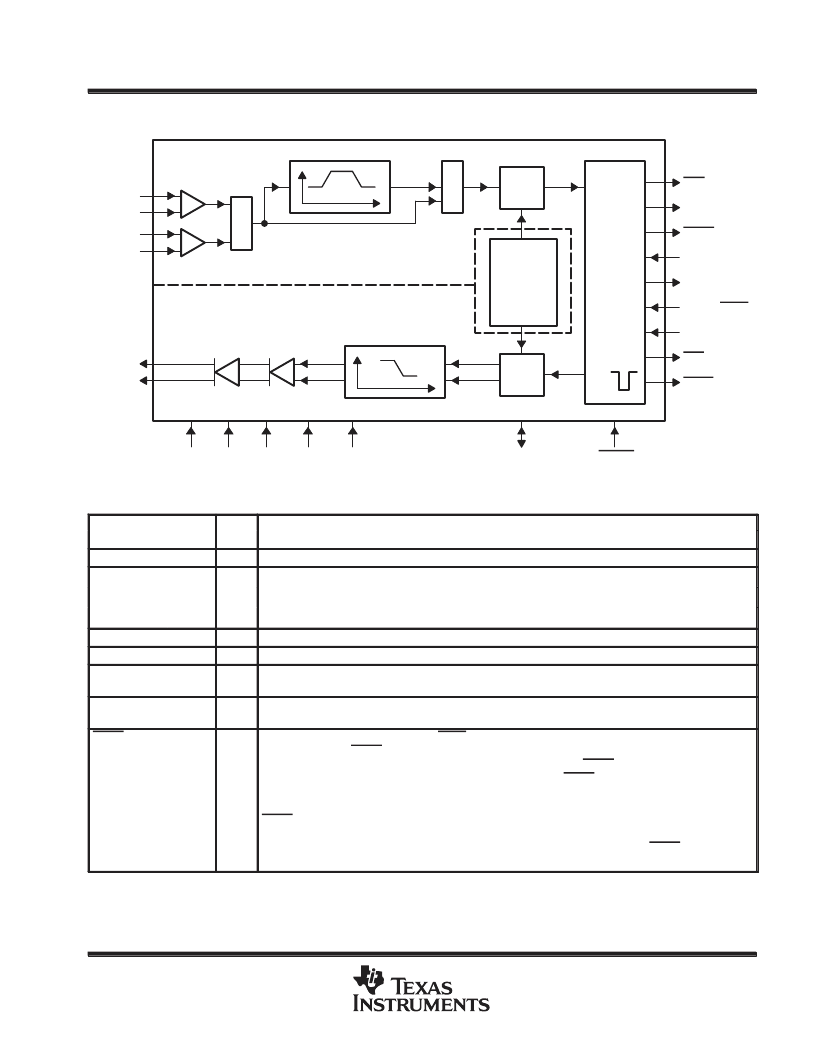

functional block diagram

M

U

X

M

U

X

IN+

IN–

AUX IN +

AUX IN –

Internal

Voltage

Reference

(TLC32040

only)

Serial

Port

A/D

OUT+

OUT–

D/A

Band-Pass Filter

Transmit Section

+

–

+

–

SHIFT CLK

MSTR CLK

EODR

DR

FSR

WORD/BYTE

DX

FSX

EODX

VCC+VCC–ANLG

GND

DTGL

GND

VDD

(DIGITAL)

REF

RESET

Low-Pass Filter

Terminal Functions

TERMINAL

NAME

ANLG GND

AUX IN+

I/O

DESCRIPTION

NO.

17,18

24

Analog ground return for all internal analog circuits. Not internally connected to DGTL GND.

Noninverting auxiliary analog input state. This input can be switched into the bandpass filter and A/D

th i

t l If th

i t bit i th

converter path via software control. If the appropriate bit in the control register is a 1, the auxiliary inputs

replace the IN+ and IN– inputs. If the bit is a 0, the IN+ and IN– inputs are used (see the AIC DX data word

re lace the IN+ and IN in uts. If the bit is a 0, the IN+ and IN in uts are used (see the AIC DX data word

format section).

I

t l

i t

1 th

AUX IN–

23

I

Inverting auxiliary analog input (see the above AUX IN+ description)

DGTL GND

9

Digital ground for all internal logic circuits. Not internally connected to ANLG GND.

DR

5

O

DR is used to transmit the ADC output bits from the AIC to the TMS320 serial port. This transmission of bits

from the AIC to the TMS320 serial port is synchronized with the SHIFT CLK signal.

DX

12

I

DX is used to receive the DAC input bits and timing and control information from the TMS320. This serial

transmission from the TMS320 serial port to the AIC is synchronized with the SHIFT CLK signal.

EODR

3

O

End of data receive. See the WORD/BYTE description and the Serial Port Timing diagrams. During the

word-mode timing, EODR is a low-going pulse that occurs immediately after the 16 bits of A/D information

have been transmitted from the AIC to the TMS320 serial port. EODR can be used to interrupt a

microprocessor upon completion of serial communications. Also, EODR can be used to strobe and enable

external serial-to-parallel shift registers, latches, or external FIFO RAM, and to facilitate parallel data bus

communications between the AIC and the serial-to-parallel shift registers. During the byte-mode timing,

EODR goes low after the first byte has been transmitted from the AIC to the TMS320 serial port and is kept

low until the second byte has been transmitted. The TMS32011 or TMS320C17 can use this low-going

signal to differentiate between the two bytes as to which is first and which is second. EODR does not occur

after secondary communication.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLC32040I | ANALOG INTERFACE CIRCUITS |

| TLC32041C | ANALOG INTERFACE CIRCUITS |

| TLC32041CFN | ANALOG INTERFACE CIRCUITS |

| TLC32041I | ANALOG INTERFACE CIRCUITS |

| TLC32040M | ANALOG INTERFACE CIRCUIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLC32040CFN | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ANALOG INTERFACE CIRCUITS |

| TLC32040CN | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ANALOG INTERFACE CIRCUITS |

| TLC32040I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ANALOG INTERFACE CIRCUITS |

| TLC32040IN | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ANALOG INTERFACE CIRCUITS |

| TLC32040M | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ANALOG INTERFACE CIRCUIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。