- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98249 > TLV1562IDW (TEXAS INSTRUMENTS INC) 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | TLV1562IDW |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| 封裝: | 1.27 MM PITCH, GREEN, SOIC-28 |

| 文件頁(yè)數(shù): | 4/41頁(yè) |

| 文件大小: | 600K |

| 代理商: | TLV1562IDW |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)

TLV1562

2.7 V TO 5.5 V, HIGH-SPEED LOW-POWER RECONFIGURABLE ANALOG-TO-DIGITAL

CONVERTER WITH 4-INPUT, DUAL S/H, PARALLEL INTERFACE, AND POWER DOWN

SLAS162 – SEPTEMBER 1998

12

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

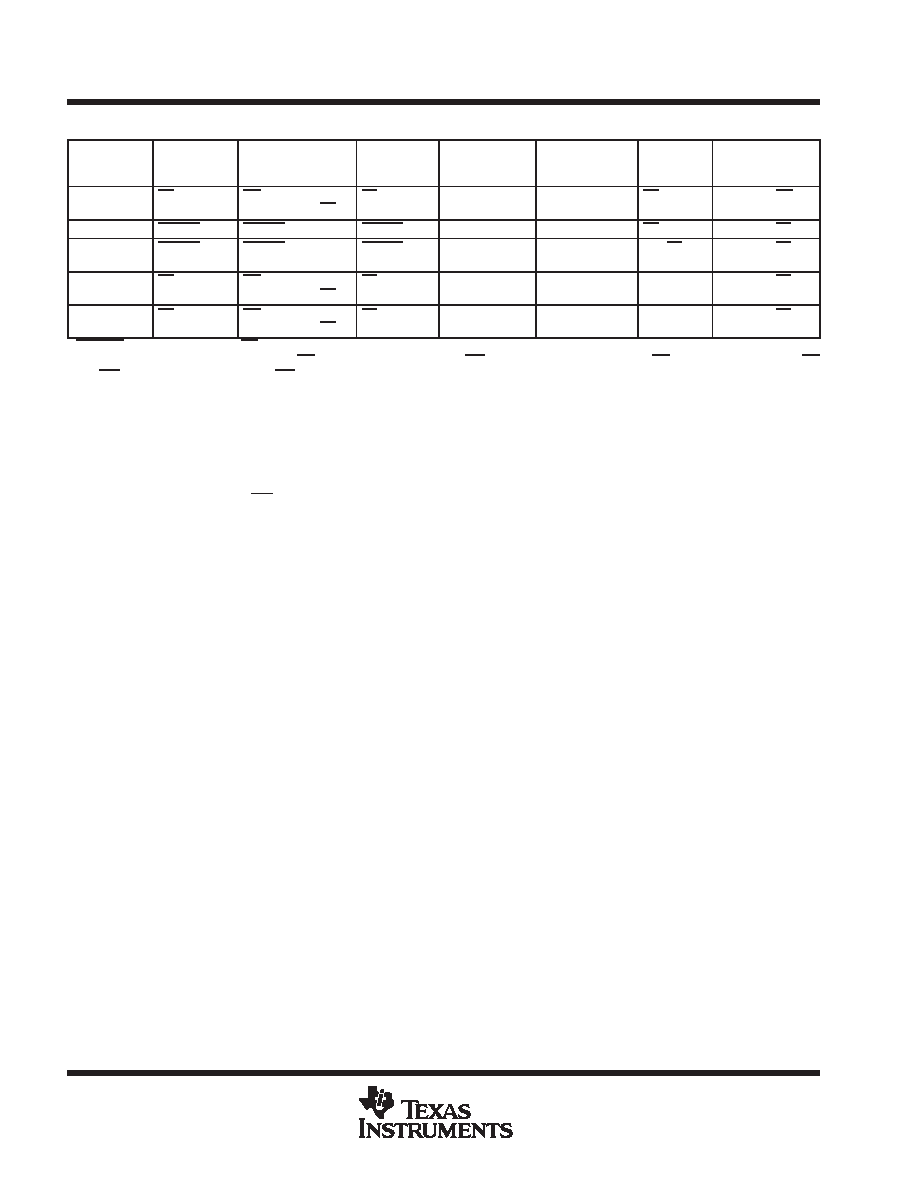

Table 2. Conversion Trigger Edge

CONVERSION

MODE

CONVERSION

TRIGGER

START OF

SAMPLING

START OF

CONVERSION

TIME

(INTERNAL CLK)

CONVERSION

TIME

(EXTERNAL CLK)

INTERRUPT

CANCELED

BY

DATA OUT

Mono

Interrupt

RD

WR

↑ or

2 SYSCLK from RD

↓

RD

↓

6 SYSCLK

5 SYSCLK

RD

↑

41 ns§ from INT low

CSTART

↓

CSTART

↑

6 SYSCLK

5 SYSCLK

RD

↓

41 ns§ from RD low

Dual

Interrupt

CSTART

↓

CSTART

↑

12 SYSCLK

10 SYSCLK

First RD

↓

41 ns§ from RD low

Mono

Continuous

RD

WR

↑ or

2 SYSCLK from RD

↓

RD

↓

6 SYSCLK

5 SYSCLK

N/A

41 ns§ from RD low

Dual

Continuous

RD

WR

↑ or

7 SYSCLK from RD

↓

RD

↓

12 SYSCLK

10 SYSCLK

N/A

41 ns§ from RD low

CSTART works with or without CS active.

The first sampling period starts at the last RD low of the previous cycle or WR high of the configuration cycle. RD low is the falling edge of RD

and WR high is the rising edge of the WR signal. (Minimum sample/hold amp settling time = one SYSCLK, approximately 100 ns min, at Rs

≤

1 k

).

§ Output data enable time is dependent on bus loading and supply voltage (BDVDD). For BDVDD = 5 V, the enable time is 19 ns at 25 pF, 23 ns

at 50 pF, and 25 ns at 100 pF. For BDVDD = 2.7 V, the enable time is 37 ns at 25 pF, 41 ns at 50 pF, and 56 ns at 100 pF.

The TLV1562 provides four types of conversion modes. The two interrupt-driven conversion modes are

asynchronous and are simple one-shot conversions. The auto-powerdown conversion feature can be enabled

when interrupt-driven conversion modes are used. The other two continuous conversion modes are

synchronous with the RD signal (as a clock) from the processor and are more suitable for repetitive signal

measurement. These different modes of conversion offer a tradeoff between simplicity and speed.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV1562IPWG4 | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TLV1562CPWLE | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TLV1562IPWLE | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TLV1562IDWRG4 | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TLV1570CPWG4 | 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV1562IDWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 2 MSPS Quad Channel RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1562IDWR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 2 MSPS Quad Channel RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1562IDWRG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 2 MSPS Quad Channel RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1562IPW | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10bit Programmable RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1562IPWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 2 MSPS Quad Channel RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。