- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98253 > TLV320AIC28IRGZRG4 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQCC48 PDF資料下載

參數(shù)資料

| 型號: | TLV320AIC28IRGZRG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| 封裝: | 7 X 7 MM, GREEN, PLASTIC, QFN-48 |

| 文件頁數(shù): | 65/85頁 |

| 文件大小: | 1053K |

| 代理商: | TLV320AIC28IRGZRG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當(dāng)前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁

TLV320AIC28

SLAS418B FEBRUARY 2004 REVISED MAY 2005

www.ti.com

68

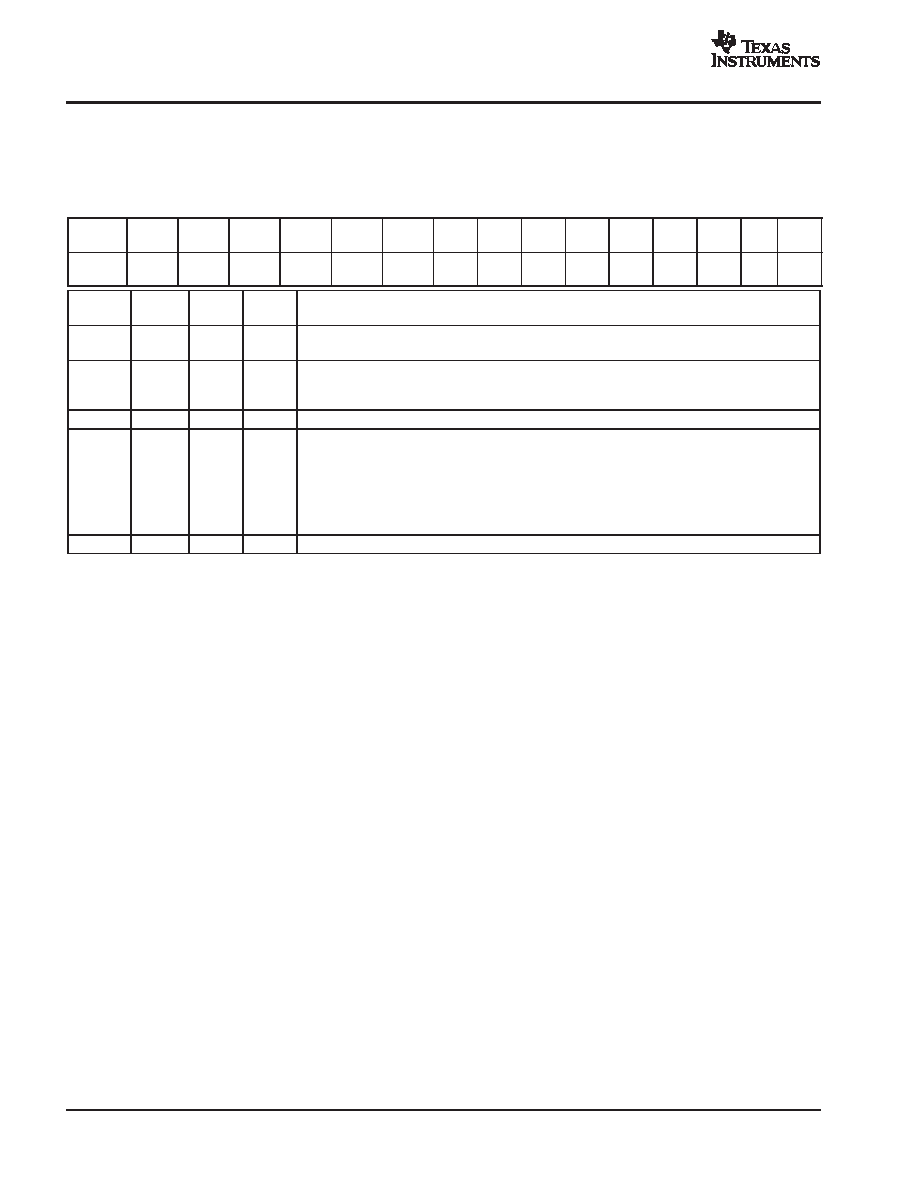

AIC28 Buffer Data Registers (Page 3)

The buffer data registers of the AIC28 hold data results from the SAR ADC conversions in buffer mode. Upon

reset, bit D15 is set to 0, bit D14 is set to 1 and the remaining bits are don’tcare. These registers are read only.

If buffer mode is enabled, then the results of all ADC conversions are placed in the buffer data register. The

data format of the result word (R) of these registers is right-justified which is as follows:

D15

MSB

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

LSB

FUF

EMF

X

ID

R11

MSB

R10

R9

R8

R7

R6

R5

R4

R3

R2

R1

R0

LSB

BIT

NAME

RESET

VALUE

READ/

WRITE

FUNCTION

D15

FUF

0

R

Buffer Full Flag

This flag indicates that all the 64 locations of the buffer are having unread data.

D14

EMF

1

R

Buffer Empty Flag

This flag indicates that there is no unread data available in FIFO. This is generated while reading the

last converted data.

D13

X

R

Reserved

D12

ID

X

R

Data Identification

0 => BAT or AUX2 data in R11R0

1 => AUX1 or TEMP data in R11R0

Order for Writing Data in Buffer When Multiple Inputs are Selected

For Auto Scan Conversion: AUX1 (if selected), AUX2 (if selected), TEMP (if selected)

For Port Scan Conversion: BAT, AUX1, AUX2

D11D0

R11R0

X’s

R

Converted Data

LAYOUT

The following layout suggestions should provide optimum performance from the AIC28. However, many

portable applications have conflicting requirements concerning power, cost, size, and weight. In general, most

portable devices have fairly clean power and grounds because most of the internal components are very low

power. This situation would mean less bypassing for the converter’s power and less concern regarding

grounding. Still, each situation is unique and the following suggestions should be reviewed carefully.

For optimum performance, care should be taken with the physical layout of the AIC28 circuitry. The basic SAR

architecture is sensitive to glitches or sudden changes on the power supply, reference, ground connections,

and digital inputs that occur just prior to latching the output of the analog comparator. Therefore, during any

single conversion for an n-bit SAR converter, there are n windows in which large external transient voltages

can easily affect the conversion result. Such glitches might originate from switching power supplies, nearby

digital logic, and high power devices. The degree of error in the digital output depends on the reference voltage,

layout, and the exact timing of the external event. The error can change if the external event changes in time

with respect to the timing of the critical n windows.

With this in mind, power to the AIC28 should be clean and well bypassed. A 0.1

F ceramic bypass capacitor

should be placed as close to the device as possible. A 1

F to 10 F capacitor may also be needed if the

impedance of the connection between the AIC28 supply pins and system power supply is high.

A bypass capacitor on the VREF pin is generally not needed because the reference is buffered by an internal

op amp, although it can be useful to reduce reference noise level. If an external reference voltage originates

from an op amp, make sure that it can drive any bypass capacitor that is used without oscillation.

The AIC28 architecture offers no inherent rejection of noise or voltage variation in regards to using an external

reference input. This is of particular concern when the reference input is tied to the power supply. Any noise

and ripple from the supply appears directly in the digital results. While high frequency noise can be filtered out,

voltage variation due to line frequency (50 Hz or 60 Hz) can be difficult to remove.

The ground pins should be connected to a clean ground point. In many cases, this is the analog ground. Avoid

connections, which are too near the grounding point of a microcontroller or digital signal processor. If needed,

run a ground trace directly from the converter to the power supply entry or battery connection point. The ideal

layout includes an analog ground plane dedicated to the converter and associated analog circuitry.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC28RGZR | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| TLV320AIC28RGZ | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| TLV320AIC28IRGZG4 | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| TLV320AIC29IRGZRG4 | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| TLV320AIC29IRGZR | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC28RGZ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STEREO AUDIO CODEC WITH INTERGRATED HEADPHONE AND SPEAKER AMPLIFIERS |

| TLV320AIC28RGZR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STEREO AUDIO CODEC WITH INTERGRATED HEADPHONE AND SPEAKER AMPLIFIERS |

| TLV320AIC29 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STEREO AUDIO CODEC WITH INTEGRATED HEADPHONE AND SPEAKER AMPLIFIERS |

| TLV320AIC29_07 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STWREO AUDIO CODEC WITH INTERGRATED HEADPHONE AND SPEAKER AMPLIFIERS |

| TLV320AIC29_08 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STEREO AUDIO CODEC WITH INTEGRATED HEADPHONE AND SPEAKER AMPLIFIERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。