- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98254 > TLV320AIC31IRHBTG4 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQCC32 PDF資料下載

參數(shù)資料

| 型號(hào): | TLV320AIC31IRHBTG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

| 封裝: | 5 X 5 MM, GREEN, PLASTIC, QFN-32 |

| 文件頁(yè)數(shù): | 38/83頁(yè) |

| 文件大小: | 1197K |

| 代理商: | TLV320AIC31IRHBTG4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)當(dāng)前第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)

www.ti.com ............................................................................................................................................. SLAS497C – AUGUST 2006 – REVISED DECEMBER 2008

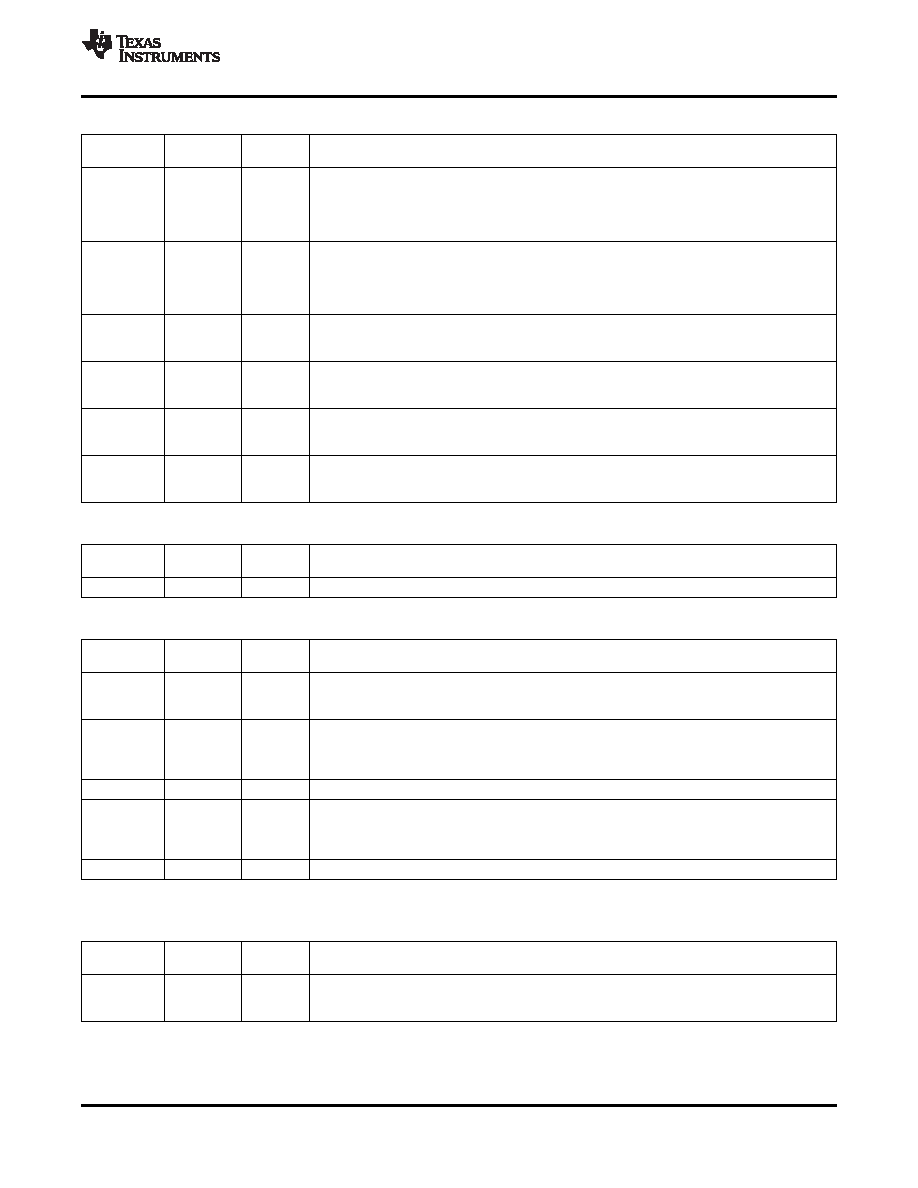

Page 0 / Register 12:

Audio Codec Digital Filter Control Register

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7–D6

R/W

00

Left ADC High-pass Filter Control

00: Left ADC High-pass filter disabled

01: Left ADC High-pass filter –3-dB frequency = 0.0045 × ADC FS

10: Left ADC High-pass filter –3-dB frequency = 0.0125 × ADC FS

11: Left ADC High-pass filter –3-dB frequency = 0.025 × ADC FS

D5–D4

R/W

00

Right ADC High-pass Filter Control

00: Right ADC High-pass filter disabled

01: Right ADC High-pass filter –3-dB frequency = 0.0045 × ADC FS

10: Right ADC High-pass filter –3-dB frequency = 0.0125 × ADC FS

11: Right ADC High-pass filter –3-dB frequency = 0.025 × ADC FS

D3

R/W

0

Left DAC Digital Effects Filter Control

0: Left DAC digital effects filter disabled (bypassed)

1: Left DAC digital effects filter enabled

D2

R/W

0

Left DAC De-emphasis Filter Control

0: Left DAC de-emphasis filter disabled (bypassed)

1: Left DAC de-emphasis filter enabled

D1

R/W

0

Right DAC Digital Effects Filter Control

0: Right DAC digital effects filter disabled (bypassed)

1: Right DAC digital effects filter enabled

D0

R/W

0

Right DAC De-emphasis Filter Control

0: Right DAC de-emphasis filter disabled (bypassed)

1: Right DAC de-emphasis filter enabled

Page 0 / Register 13:

Reserved

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7–D0

R/W

00000000

Reserved. Write only '00000000' to this register.

Page 0 / Register 14:

Headset Configuration Register

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7

R/W

0

Driver Capacitive Coupling

0: Programs high-power outputs for capless driver configuration

1: Programs high-power outputs for ac-coupled driver configuration

D6(1)

R/W

0

Stereo Output Driver Configuration A

Note: do not set bits D6 and D3 both high at the same time.

0: A stereo fully-differential output configuration is not being used

1: A stereo fully-differential output configuration is being used

D5–D4

R

00

Reserved. Write only '00' to these bits.

D3(1)

R/W

0

Stereo Output Driver Configuration B

Note: do not set bits D6 and D3 both high at the same time.

0: A stereo pseudo-differential output configuration is not being used

1: A stereo pseudo-differential output configuration is being used

D2–D0

R

000

Reserved. Write only 0s to these bits.

(1)

Do not set D6 and D3 to 1 simultaneously

Page 0 / Register 15:

Left ADC PGA Gain Control Register

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7

R/W

1

Left ADC PGA Mute

0: The left ADC PGA is not muted

1: The left ADC PGA is muted

Copyright 2006–2008, Texas Instruments Incorporated

43

Product Folder Link(s): TLV320AIC31

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC31IRHBT | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

| TLV320AIC3253IRGER | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

| TLV320AIC3253IRGET | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

| TLV320AIC3253IYZKR | SPECIALTY CONSUMER CIRCUIT, BGA25 |

| TLV320AIC3253IYZKT | SPECIALTY CONSUMER CIRCUIT, BGA25 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC32 | 制造商:BB 制造商全稱:BB 功能描述:LOW POWER STEREO AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY |

| TLV320AIC32_07 | 制造商:BB 制造商全稱:BB 功能描述:LOW POWER STEREO AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY |

| TLV320AIC3204 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Ultra Low Power Stereo Audio Codec |

| TLV320AIC3204EVM-K | 功能描述:音頻 IC 開發(fā)工具 TLV320AIC3204 Eval Kit RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評(píng)估:TAS5614L 工作電源電壓:12 V to 38 V |

| TLV320AIC3204IRHBR | 功能描述:接口—CODEC Very LW PWR Stereo Audio CODEC/TuneTM RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。