- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98281 > TPS40070PWPRG4 (TEXAS INSTRUMENTS INC) 2 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | TPS40070PWPRG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 穩(wěn)壓器 |

| 英文描述: | 2 A SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, PDSO16 |

| 封裝: | GREEN, PLASTIC, HTSSOP-16 |

| 文件頁數(shù): | 7/28頁 |

| 文件大小: | 655K |

| 代理商: | TPS40070PWPRG4 |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

VDG03174

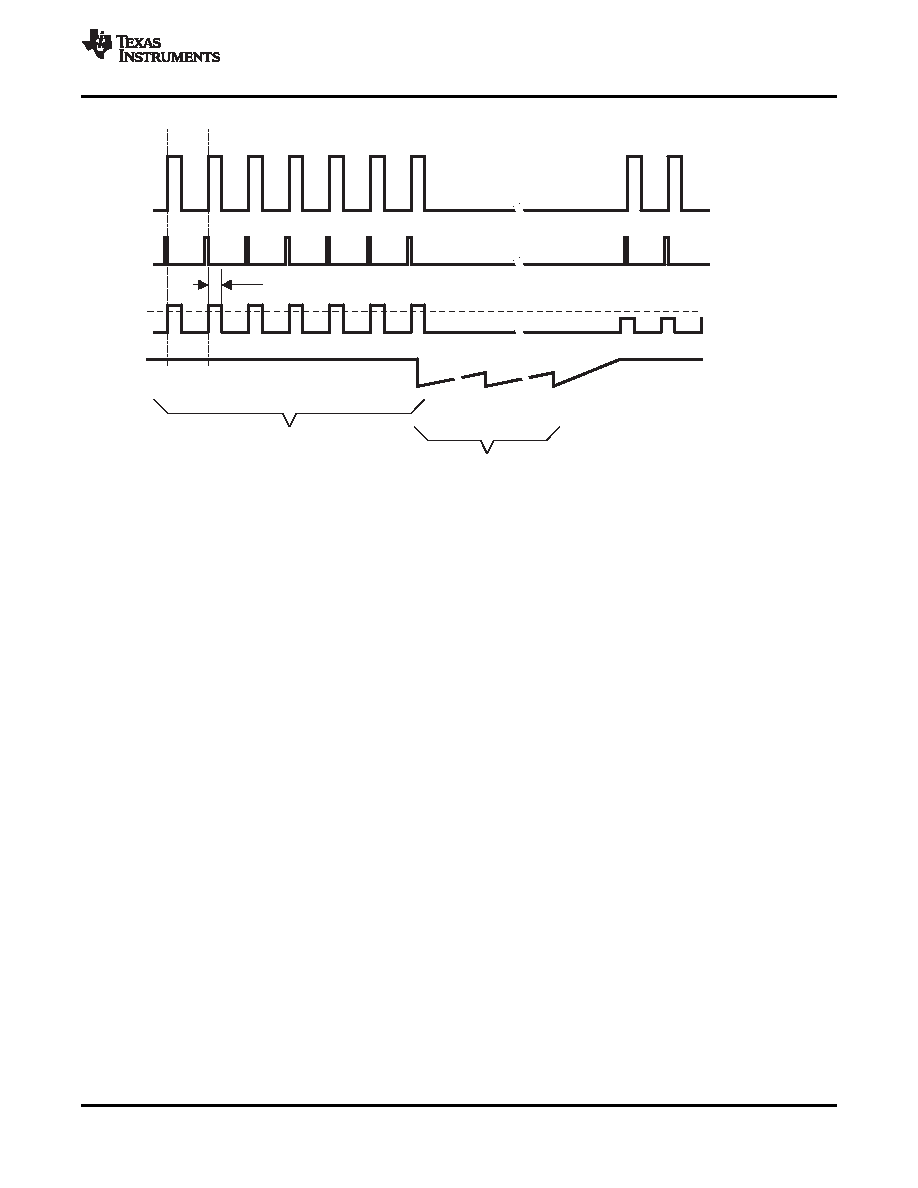

tBLANKING

7 Current-Limit Trips

(HDRV Cycle Terminated by Current-Limit Trip)

7

Soft-Start

Cycles

HDRV

Clock

VILIM

VVIN VSW

SS

LOOP COMPENSATION

K

PWM ^ VUVLO (on)

(14)

www.ti.com .................................................................................................................................................. SLUS582J – DECEMBER 2003 – REVISED APRIL 2009

Figure 11. Typical Fault Protection Waveforms

Voltage mode buck type converters are typically compensated using Type III networks. Since the TPS4007x

uses voltage feedforward control, the gain of the voltage feedforward circuit must be included in the PWM gain.

The gain of the voltage feedforward circuit combined with the PWM circuit and power stage for the TPS4007x is:

The remainder of the loop compensation is performed as in a normal buck converter. Note that the voltage

feedforward circuitry removes the input voltage term from the expression for PWM gain. PWM gain is strictly a

function of the programmed startup voltage.

Copyright 2003–2009, Texas Instruments Incorporated

15

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。