- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373713 > TS68040MR25A (ATMEL CORP) Third- Generation 32-bit Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | TS68040MR25A |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Third- Generation 32-bit Microprocessor |

| 中文描述: | 32-BIT, 25 MHz, MICROPROCESSOR, CPGA179 |

| 封裝: | CERAMIC, PGA-179 |

| 文件頁數(shù): | 20/49頁 |

| 文件大小: | 1637K |

| 代理商: | TS68040MR25A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

20

TS68040

2116A–HIREL–09/02

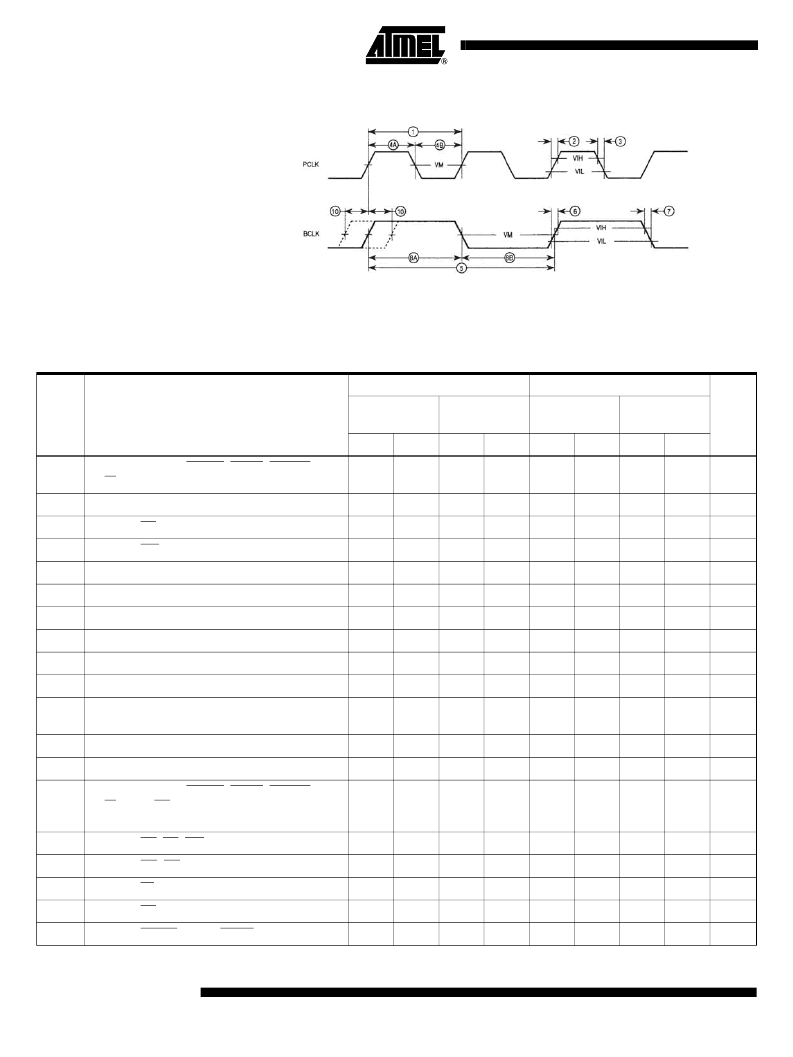

Figure 8.

Clock Input Timing

Table 14.

Output AC Timing Specifications

(1)

(Figure 9 to Figure 15)

These output specifications are only for 25 MHz. They must be scaled for lower operating frequencies. Refer to

TS6804DH/AD for further information. -55°C

≤

T

C

≤

T

Jmax

; 4.75V

≤

V

CC

≤

5.25V unless otherwise specified.

(2)(3)(4)

Num

Characteristic

25 MHz

33 MHz

Unit

Large

Buffer

(1)

Small

Buffer

(1)

Large

Buffer

(1)

Small

Buffer

(1)

Min

Max

Min

Max

Min

Max

Min

Max

11

BCLK to address CIOUT, LOCK, LOCKE,

R/W, SIZn, TLN, TMn, UPAn valid

(5)

9

21

9

30

6.50

18

6.50

25

ns

12

BCLK to output invalid (output hold)

9

9

6.50

6.50

ns

13

BCLK to TS valid

9

21

9

30

6.50

18

6.50

25

ns

14

BCLK to TIP valid

9

21

9

30

6.50

18

6.50

25

ns

18

BCLK to data-out valid

(6)

9

23

9

32

6.50

20

6.50

27

ns

19

BCLK to data-out invalid (output hold)

(6)

9

9

6.50

6.50

ns

20

BCLK to output low impedance

(5)(6)

9

9

6.50

6.50

ns

21

BCLK to data-out high impedance

9

20

9

20

6.50

17

6.50

17

ns

26

BCLK to multiplexed address valid

(5)

19

31

19

40

14

26

14

33

ns

27

BCLK to multiplexed address driven

(5)

19

19

14

14

ns

28

BCLK to multiplexed address high

impedance

(5)(6)

9

18

9

18

6.50

15

6.50

15

ns

29

BCLK to multiplexed data driven

(6)

19

19

14

20

14

20

ns

30

BCLK to multiplexed data valid

(6)

19

33

19

42

14

28

14

35

ns

38

BCLK to address CIOUT, LOCK, LOCKE,

R/W, SIZn, TS, TLNn, TMn, TTn, UPAn high

impedance

(5)

9

18

9

18

6.50

15

6.50

15

ns

39

BCLK to BB, TA, TIP high impedance

19

28

19

28

14

23

14

23

ns

40

BCLK to BR, BB valid

9

21

9

30

6.50

18

6.50

25

ns

43

BCLK to MI valid

9

21

9

30

6.50

18

6.50

25

ns

48

BCLK to TA valid

9

21

9

30

6.50

18

6.50

25

ns

50

BCLK to IPEND, PSTn, RSTO valid

9

21

9

30

6.50

18

6.50

25

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS68040VF25A | Third- Generation 32-bit Microprocessor |

| TS68230CFN10 | HMOS PARALLEL INTERFACE/TIMER |

| TS68230FN | HMOS PARALLEL INTERFACE/TIMER |

| TS68230 | HMOS PARALLEL INTERFACE/TIMER |

| TS68230CP10 | HMOS PARALLEL INTERFACE/TIMER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS68040MR33A | 制造商:e2v technologies 功能描述:MPU TS68000 32BIT HCMOS 33MHZ 179PIN PGA - Trays |

| TS68040MRB/C25A | 制造商:e2v Aerospace & Defense 功能描述:MPU TS68000 32-Bit HCMOS 25MHz 179-Pin PGA 制造商:e2v technologies 功能描述:TS68040MRB/C25A - Rail/Tube 制造商:e2v technologies 功能描述:5962-9314301MXC - Rail/Tube |

| TS68040MRB/C33A | 制造商:e2v technologies 功能描述:TS68040MRB/C33A - Rail/Tube |

| TS68040MRD/T25A | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Third- Generation 32-bit Microprocessor |

| TS68040MRD/T33A | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Third- Generation 32-bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。