- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373714 > TS68332DESC01ZC (ATMEL CORP) High performance 32-bit integrated microcontroller PDF資料下載

參數(shù)資料

| 型號: | TS68332DESC01ZC |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | High performance 32-bit integrated microcontroller |

| 中文描述: | 32-BIT, 16.78 MHz, MICROCONTROLLER, CPGA132 |

| 封裝: | CERAMIC, PGA-132 |

| 文件頁數(shù): | 35/56頁 |

| 文件大?。?/td> | 1510K |

| 代理商: | TS68332DESC01ZC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

35

TS68332

2118A–HIREL–03/02

BusControlSignals

TheMCUinitiatesabuscyclebydrivingtheaddress,size,function,code,and

read/writeoutputs.Atthebeginningofabuscycle,thesizesignals(SIZ1,SIZ0)are

drivenalongwiththefunctioncodesignals.SIZ1andSIZ0indicatethenumberofbytes

remainingtobetransferredduringanoperandcycle(consistingofoneormorebus

cycles).Table8showstheencodingofSIZ1andSIZ0.Theread/write(R/W)signal

determinesthedirectionofthetransferduringabuscycle.Theread-modify-writecycle

signal(RMC)isassertedatthebeginningofthefirstbuscycleofaread-modify-write

operation,andremainsasserteduntilcompletionofthefinalbuscycleoftheoperation.

BusCycleTermination

Signals

Duringbuscycles,externaldevicesassertthedatatransferandsizeacknowledgesig-

nalsDSACK1and/orDSACK0aspartofthebusprotocol.Duringareadcycle,this

signalstheMCUtoterminatethebuscycleandtolatchthedata.Duringawritecycle,

thisindicatesthattheexternaldevicehassuccessfullystoredthedataandthatthecycle

mayterminate.ThesesignalsalsoindicatetotheMCUthesizeoftheportforthebus

cyclejustcompleted.

Thebuserror(BERR)signalisalsoabuscycleterminationindicatorandcanbeusedin

theabsenceofDSACKxtoindicateabuserrorcondition.Itcanalsobeassertedincon-

junctionwithDSACKxtoindicateabuserrorcondition,provideditmeetsthe

appropriatetiming.Additionally,theBERRandHALTsignalscanbeassertedsimulta-

neously,inlieuof,orinconjunctionwith,theDSACKxsignals.

TheinternalbusmonitorcanbeusedtogeneratetheBERRsignalforinternalandinter-

nal-to-externaltransfers.AnexternalbusmastermustprovideitsownBERRgeneration

anddrivetheBERRpin,sincetheinternalBERRmonitorhasnoinformationabout

transfersinitiatedbyanexternalbusmaster.

Finally,theautovector(AVEC)signalcanbeusedtoterminateinterruptacknowledge

cycles,indicatingthattheMCUshouldinternallygenerateavectornumbertolocatean

interrupthandlerroutine.AVECisignoredduringallotherbuscycles.

DynamicBusSizing

TheMCUdynamicallyinterruptstheportsizeoftheaddresseddeviceduringeachbus

signal,allowingoperandtransferstoorfrom8-and16-bitports.Duringanoperand

transfercycle,theslavedevicesignalsitsportsize(byteorword)andindicatescomple-

tionofthebuscycletotheMCUthroughtheuseoftheDSACKxencodingsand

assertionresults.RefertoTable9forDSACKxencodingsandassertionresults.For

example,iftheMCUisexecutinganinstructionthatreadsalong-wordoperandfroma

16-bitport,theMCUlatchesthe16bitsofvaliddataandrunsanotherbuscycleto

obtaintheother16bits.

Dynamicbussizingrequiresthattheportionofthedatabusforatransfertoorfroma

particularportsizebefixed.Forexamplean8-bitportmustresideondatabusbits15-

8.

TheSIZxsignalsalsoformpartofthebussizingprotocol.Theseoutputsindicatethe

remainingnumberorbytestobetransferredduringthecurrentbuscycle.

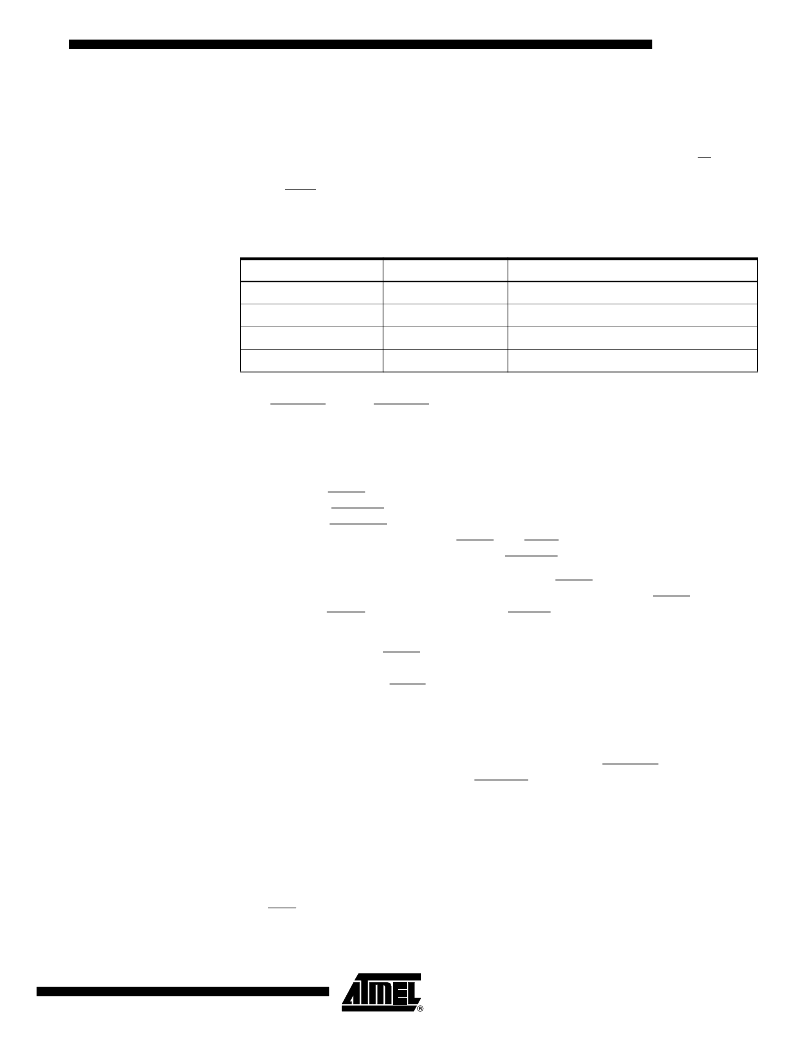

Table8.

SizeSignalEncoding

SIZ1

SIZ2

TransferSize

0

1

Byte

1

0

Word

1

1

3Byte

0

0

LongWord

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS68332DESC02XA | High performance 32-bit integrated microcontroller |

| TS68332DESC02ZC | High performance 32-bit integrated microcontroller |

| TS68332MA16 | High performance 32-bit integrated microcontroller |

| TS68332MA20 | High performance 32-bit integrated microcontroller |

| TS68332MR16 | High performance 32-bit integrated microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS68332DESC02XA | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:High performance 32-bit integrated microcontroller |

| TS68332DESC02ZC | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:High performance 32-bit integrated microcontroller |

| TS68332MA16 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:High performance 32-bit integrated microcontroller |

| TS68332MA20 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:High performance 32-bit integrated microcontroller |

| TS68332MA20A | 制造商:e2v technologies 功能描述:TS68332MA20A - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。