- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98307 > TVP7002PZPR (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | TVP7002PZPR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | GREEN, PLASTIC, HTQFP-100 |

| 文件頁數(shù): | 21/57頁 |

| 文件大小: | 517K |

| 代理商: | TVP7002PZPR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

SLES206B

– MAY 2007 – REVISED MAY 2011

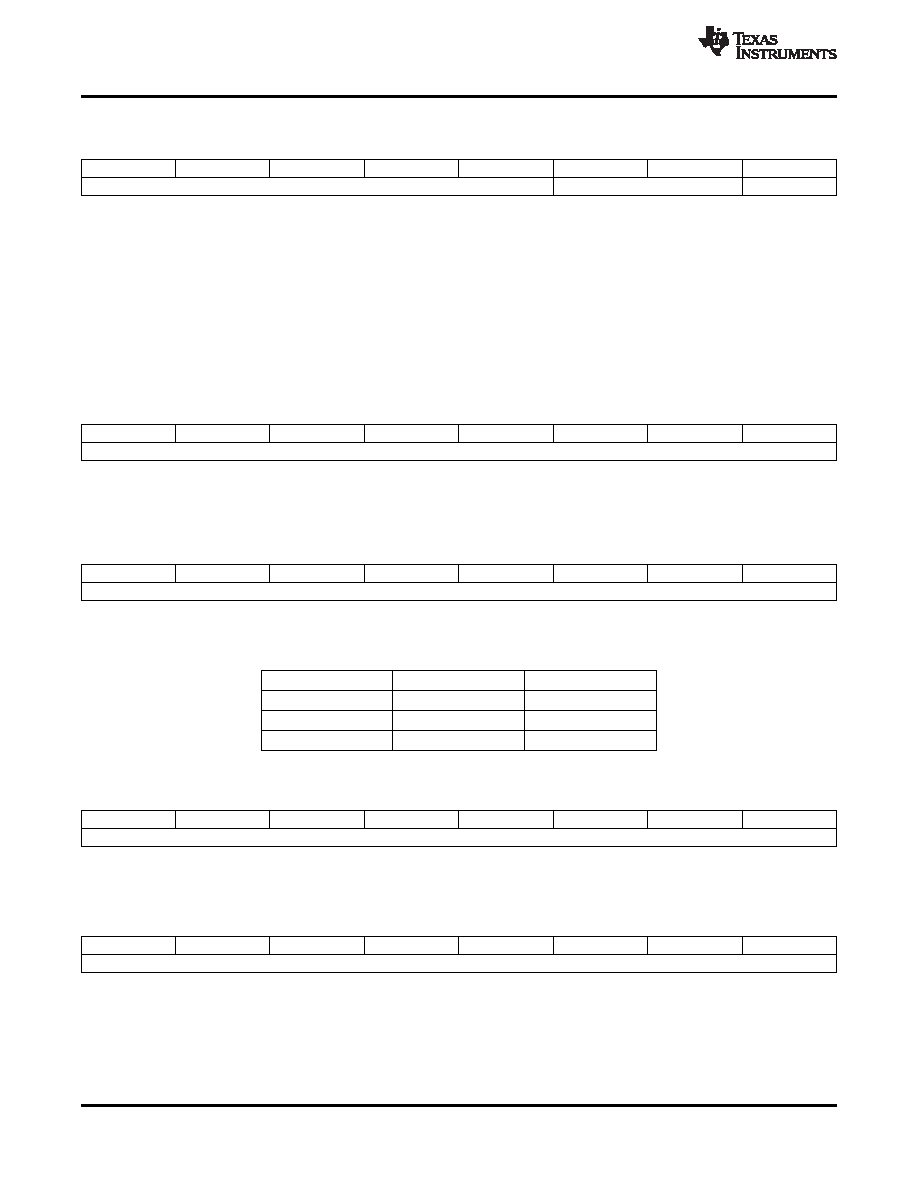

H-PLL Phase Select

Subaddress

04h

Default (80h)

7

6

5

4

3

2

1

0

Phase Select [4:0]

Reserved

DIV2

Phase Select [4:0]: ADC sampling clock phase select. (1 LSB = 360/32 = 11.25

°). A host-based automatic phase control algorithm can be

used to control this setting to optimize graphics sampling phase.

00h = 0 degrees

10h = 180 degrees (default)

1Fh = 348.75 degrees

DIV2: DATACLK divide-by-2. H-PLL post divider. May be used with a 2x H-PLL feedback divider to improve jitter at low frequencies. When

used, only half of the Phase Select [4:0] settings are functional.

0 = DATACLK/1 (default)

1 = DATACLK/2

Clamp Start

Subaddress

05h

Default (32h)

7

6

5

4

3

2

1

0

Clamp Start [7:0]

Clamp Start [7:0]: Positions the clamp signal an integer number of clock periods after the HSYNC signal. If external clamping is selected

this value has no meaning. Clamp Start must be correctly positioned for proper operation. See Table 13 for the recommended settings.

Clamp Width

Subaddress

06h

Default (20h)

7

6

5

4

3

2

1

0

Clamp Width [7:0]

Clamp Width [7:0]: Sets the width in pixels for the fine clamp. See also register Clamp Start (subaddress 05h).

Table 13. Recommended Fine Clamp Settings

VIDEO STANDARD

CLAMP START

CLAMP WIDTH

HDTV (tri-level)

50 (32h)

32 (20h)

SDTV (bi-level)

6 (06h)

16 (10h)

PC graphics

6 (06h)

16 (10h)

HSYNC Output Width

Subaddress

07h

Default (20h)

7

6

5

4

3

2

1

0

HSOUT Width [7:0]

HSOUT Width [7:0]: Sets the width in pixels for HSYNC output.

Blue Fine Gain

Subaddress

08h

Default (00h)

7

6

5

4

3

2

1

0

Blue Fine Gain [7:0]

Blue Fine Gain [7:0]: 8-bit fine digital gain (contrast) for Blue channel (applied after the ADC). Offset binary value.

Blue Fine Gain = 1 + Blue Fine Gain [7:0]/256

Blue Fine Gain [7:0]

Blue Fine Gain

00h

1.0 (default)

80h

1.5

FFh

2.0

28

Copyright

2007–2011, Texas Instruments Incorporated

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TVP7002PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TWL1101PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TWL1101PFBR | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TWL1102PBS | SPECIALTY CONSUMER CIRCUIT, PQFP32 |

| TWL1102PBSR | SPECIALTY CONSUMER CIRCUIT, PQFP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TVP9000MZDSR | 制造商:Texas Instruments 功能描述: |

| TVP9000ZDS | 制造商:Texas Instruments 功能描述: |

| TVP9000ZDSR | 制造商:Texas Instruments 功能描述: |

| TVP9001ZDS | 制造商:Texas Instruments 功能描述: |

| TVP9001ZDSR | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。