- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98307 > TWL2214CAPFB (TEXAS INSTRUMENTS INC) 1-CHANNEL POWER SUPPLY SUPPORT CKT, PQFP48 PDF資料下載

參數(shù)資料

| 型號(hào): | TWL2214CAPFB |

| 廠(chǎng)商: | TEXAS INSTRUMENTS INC |

| 元件分類(lèi): | 電源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PQFP48 |

| 封裝: | PLASTIC, TQFP-48 |

| 文件頁(yè)數(shù): | 6/39頁(yè) |

| 文件大小: | 583K |

| 代理商: | TWL2214CAPFB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)

TWL2214CA

POWER SUPPLY MANAGEMENT IC AND

LiIon BATTERY CHARGE CONTROL

SLVS321A – OCTOBER 2001 – REVISED JANUARY 2002

14

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

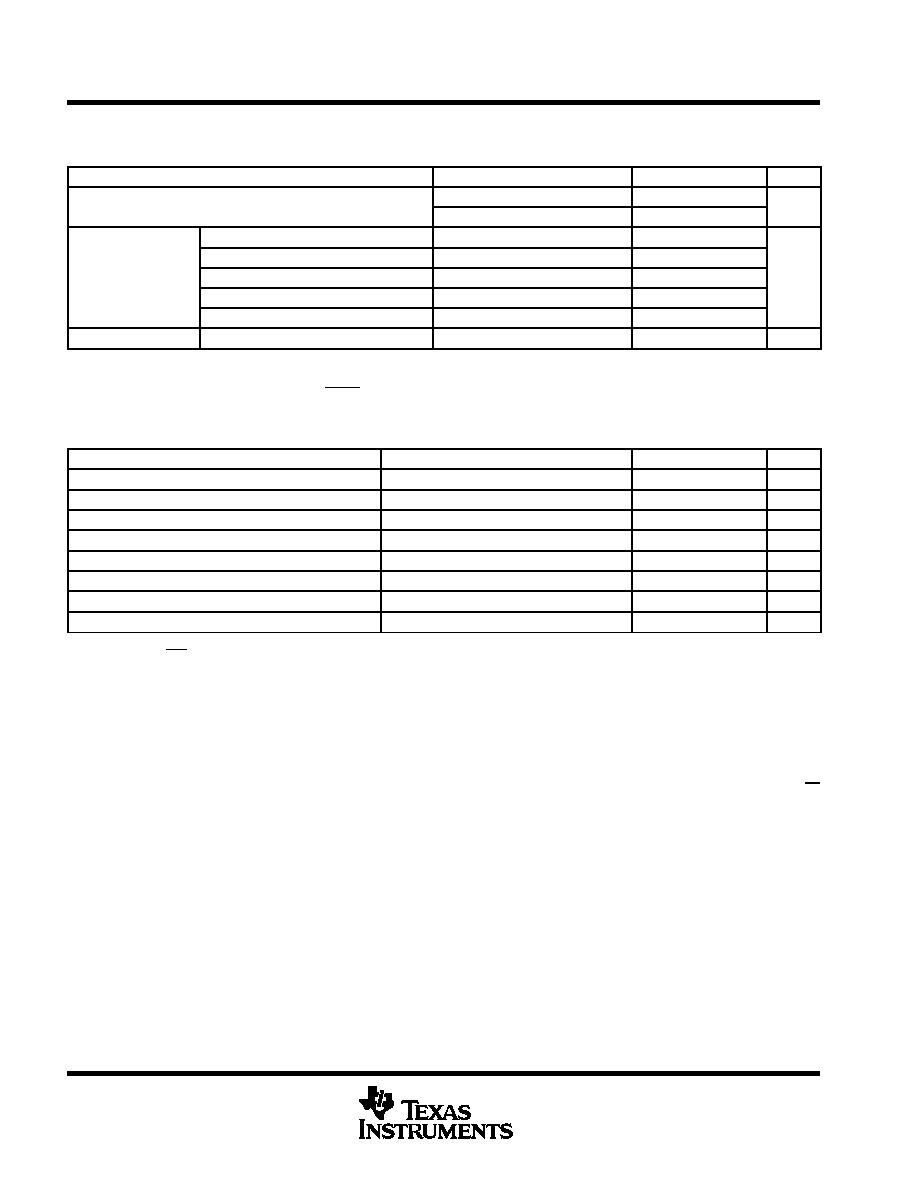

electrical characteristics, TA = –25°C to 85°C (unless otherwise noted) (continued)

battery charger control (continued)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

V

reg lation (CV)

VBREG = 4.1 V

4.059

4.1

4.141

V

VBAT regulation (CV)

VBREG = 4.2 V

4.158

4.2

4.242

V

Low voltage cutoff

1.9

High voltage cutoff

4.45

VBAT

Fast charge voltage

3.2

V

VBAT

Precharge voltage

(see Note 5)

1.9

2.05

2.2

V

Pack wake-up voltage

4.214

4.30

4.386

ICC

Operating current

20

mA

VBREG is the regulated battery voltage programmed by setting bit 1 of CSV register.

NOTES:

5. Precharge current set by I

PRE +

V

PRE

R

PR

45

where V

PRE +

1.2 V

" 10%

ADC specification

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Resolution

Output impedance <100 k

8

bit

Integral nonlinearity

Confirm monotonous (see Note 6)

–1

1

LSB

Low-level input

ADC output = 00H

0

0.1

V

High-level input

ADC output = FFH

1.9

2

2.1

V

Input capacitance

3

pF

ADC CLK

450

500

550

kHz

AD conversion time, tC

From the start of SETUP

16

CLK

Power-up time

From the ADEN up selection

10

s

NOTE 6: LSB

+ 2V

255

+ 7.8 mV

DISB interface

The TWL2214CA device supports both I2C bus and SPI bus serial interfaces. The interface uses serial data

(DATA) and serial clock (CLK) to carry information between the devices. The CE terminal (A8) in the GQE

package selects I2C or SPI. The device that initiates a transfer, generates clock signals, and terminates a

transfer is the master. The TWL2214CA device operates as a slave device. The slave address for this device

is fixed at E4h for write operations and E5h for read operations. The LSB of this slave address is simply an R/W

flag. DATA is a bidirectional line connected to VREG1 via a 10-k pullup resistor. Data can be transferred at a

rate up to 400K bits/s for I2C and up to 2M bits/s for SPI with one clock pulse generated for each data bit

transferred. MSB is transferred first. When the bus is free, both DATA and CLK are high. Data transfer can only

be initiated when the bus is free. The bus must return to the free state when the transfer is complete. Failure

to return to the free state may cause an error.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TX810IRHHT | SPECIALTY ANALOG CIRCUIT, PQCC36 |

| TX810IRHHR | SPECIALTY ANALOG CIRCUIT, PQCC36 |

| TZA1031HL | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TZA1045TM | SPECIALTY CONSUMER CIRCUIT, PDSO16 |

| TZA1047HL/M1B | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TWL2214CAPFBR | 制造商:Rochester Electronics LLC 功能描述:POWER SUPPLY MANAGEMENT IC:LION - Bulk 制造商:Texas Instruments 功能描述:CHGR LI-ION/LI-POL 150MA 2.8V 48TQFP - Tape and Reel |

| TWL2217CGGMR | 制造商:Texas Instruments 功能描述: |

| TWL2217CZQER | 制造商:Texas Instruments 功能描述: |

| TWL3014CGGMR | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TWL3016B2ZQW | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。