- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384045 > UPD72871FA2 (NEC Corp.) IEEE1394 1-CHIP OHCI HOST CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | UPD72871FA2 |

| 廠商: | NEC Corp. |

| 英文描述: | IEEE1394 1-CHIP OHCI HOST CONTROLLER |

| 中文描述: | IEEE1394連接1 - OHCI主機控制器芯片 |

| 文件頁數(shù): | 28/48頁 |

| 文件大小: | 311K |

| 代理商: | UPD72871FA2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

Preliminary Data Sheet S13925EJ2V0DS00

28

μ

PD72870,72871

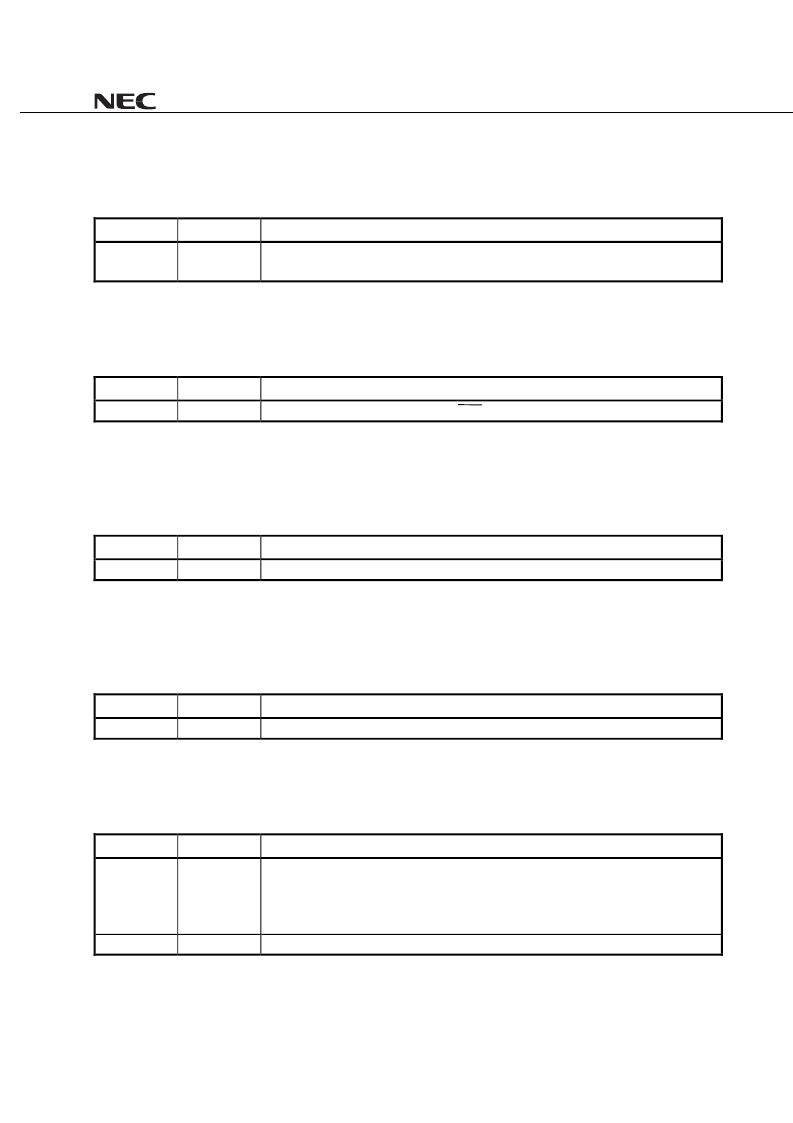

3.1.16 Offset_3C Interrupt Line Register

This register provides the interrupt line routing information specific to the

μ

PD72870, 72871, the NEC’s

implementation of the 1394 OpenHCI specification.

Bits

R/W

Description

7-0

R/W

Default value of 00H. It specifies which input of the host system interrupt controller the

interrupt pin of the

μ

PD72870, 72871 is connected to.

3.1.17 Offset_3D Interrupt Pin Register

This register provides the interrupt line routing information specific to the

μ

PD72870, 72871, the NEC’s

implementation of the 1394 OpenHCI specification.

Bits

R/W

Description

7-0

R

Constant value of 01H. It specifies PCI INTA is used for interrupting the host system.

3.1.18 Offset_3E Min_Grant Register

This register specifies how long of a burst period the

μ

PD72870, 72871 needs, assuming a clock rate of 33MHz.

Resolution is in units of

μ

s. The value should be loaded into the register from the external serial EEPROM upon

power-up reset, and access to this register through PCI-bus is prohibited.

Bits

R/W

Description

7-0

R

Default value of 00H. Its value contributes to the desired setting for Latency Timer value.

3.1.19 Offset_3F Max Lat Register

This register specifies how often the

μ

PD72870, 72871 needs to gain access to the PCI-bus, assuming a clock

rate of 33MHz. Resolution is in units of

μ

s. The value should be loaded into the register from the external serial

EEPROM after hardware reset, and access to this register through PCI-bus is prohibited.

Bits

R/W

Description

7-0

R

Default value of 00H. Its value contributes to the desired setting for Latency Timer value.

3.1.20 Offset_40 PCI_OHCI_Control Register

This register specifies the control bits that are IEEE1394 OpenHCI specific. Vendor options are not allowed in this

register. It is reserved for OpenHCI use only.

Bits

R/W

Description

0

R/W

PCI global SWAP

Default value of 0. When this bit is 1, all quadrates read from and written to

the PCI Interface are byte swapped, thus a “PCI Global Swap”. PCI addresses for expansion

ROM and PCI Configuration registers, are, however, unaffected by this bit. This bit is not

required for motherboard implementations.

31-1

R

Reserved

Constant value of all 0.

相關PDF資料 |

PDF描述 |

|---|---|

| UPD72873 | MOS INTEGRATED CIRCUIT |

| UPD72873GC-YEB | MOS INTEGRATED CIRCUIT |

| UPD72874 | IEEE1394 OHCI 1.1 COMPLIANT 3PORT PHY-LINK 1-CHIP HOST CONTROLLER |

| UPD72874GC-YEB | IEEE1394 OHCI 1.1 COMPLIANT 3PORT PHY-LINK 1-CHIP HOST CONTROLLER |

| UPD7281 | IEEE1394 OHCI 1.1 COMPLIANT 3PORT PHY-LINK 1-CHIP HOST CONTROLLER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| UPD74HC04C | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD750068GT-396 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7507C189 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD7508CU265 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。