- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378746 > UPD750104 (NEC Corp.) 4 BIT SINGLE-CHIP MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | UPD750104 |

| 廠商: | NEC Corp. |

| 英文描述: | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| 中文描述: | 4位單片機(jī) |

| 文件頁數(shù): | 37/80頁 |

| 文件大小: | 525K |

| 代理商: | UPD750104 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

37

μ

PD750104, 750106, 750108, 750104(A), 750106(A), 750108(A)

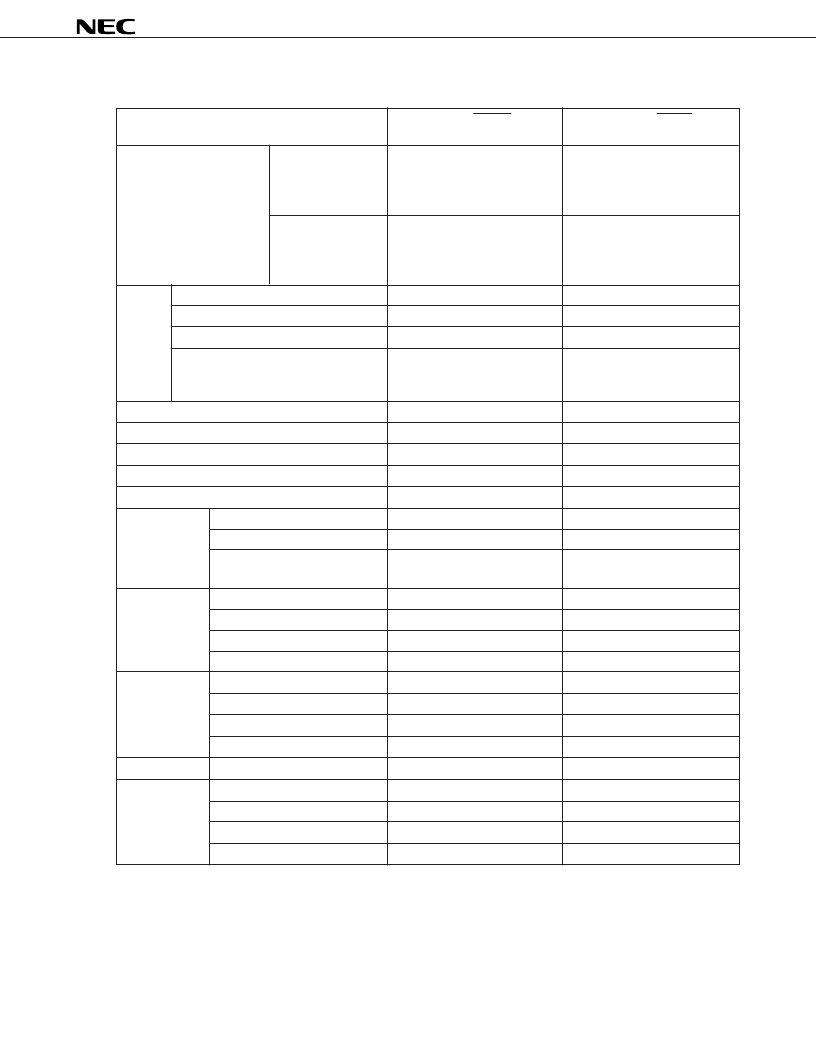

Table 9-1. Status of the Hardware after a Reset (1/2)

Program counter (PC)

PSW

Stack pointer (SP)

Stack bank selection register (SBS)

Data memory (RAM)

General-purpose registers (X, A, H, L, D, E, B, C)

Bank selection register (MBS, RBS)

Timer/event

counter

Timer counter

Clock timer

Serial interface

4 low-order bits at address 0000H

in program memory are set in PC

bits 11 to 8, and the data at address

0001H are set in PC bits 7 to 0.

5 low-order bits at address 0000H

in program memory are set in PC

bits 12 to 8, and the data at address

0001H are set in PC bits 7 to 0.

Held

0

0

Bit 6 at address 0000H in

program memory is set in RBE,

and bit 7 is set in MBE.

Undefined

1000B

Held

Held

0, 0

Undefined

0

0

0

FFH

0

0, 0

0

FFH

0

0, 0

0

Held

0

0

Held

4 low-order bits at address 0000H

in program memory are set in PC

bits 11 to 8, and the data at address

0001H are set in PC bits 7 to 0.

5 low-order bits at address 0000H

in program memory are set in PC

bits 12 to 8, and the data at address

0001H are set in PC bits 7 to 0.

Undefined

0

0

Bit 6 at address 0000H in program

memory is set in RBE, and bit 7 is

set in MBE.

Undefined

1000B

Undefined

Undefined

0, 0

Undefined

0

0

0

FFH

0

0, 0

0

FFH

0

0, 0

0

Undefined

0

0

Undefined

Generation of a RESET signal

during operation

Generation of a RESET signal in

a standby mode

Hardware

Carry flag (CY)

Skip flags (SK0 to SK2)

Interrupt status flags (IST0, IST1)

Bank enable flags (MBE, RBE)

μ

PD750104

μ

PD750106, 750108

Counter (BT)

Mode register (BTM)

Watchdog timer enable flag

(WDTM)

Counter (T0)

Modulo register (TMOD0)

Mode register (TM0)

TOE0, TOUT flip-flop

Counter (T1)

Modulo register (TMOD1)

Mode register (TM1)

TOE1, TOUT flip-flop

Mode register (WM)

Shift register (SIO)

Operation mode register (CSIM)

SBI control register (SBIC)

Slave address register (SVA)

Basic interval

timer/ watchdog

timer

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD750104A | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| UPD750104CU | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| UPD750104CUA | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| UPD750104GB | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| UPD750104GBA | 4 BIT SINGLE-CHIP MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD7507C189 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD7508CU265 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD753012AGC-P33-8BT-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD753016AGC-P29-8BT | 制造商:Renesas Electronics Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。