- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378746 > UPD750106CU (NEC Corp.) 4 BIT SINGLE-CHIP MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | UPD750106CU |

| 廠商: | NEC Corp. |

| 英文描述: | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| 中文描述: | 4位單片機 |

| 文件頁數(shù): | 10/80頁 |

| 文件大小: | 525K |

| 代理商: | UPD750106CU |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

μ

PD750104, 750106, 750108, 750104(A), 750106(A), 750108(A)

10

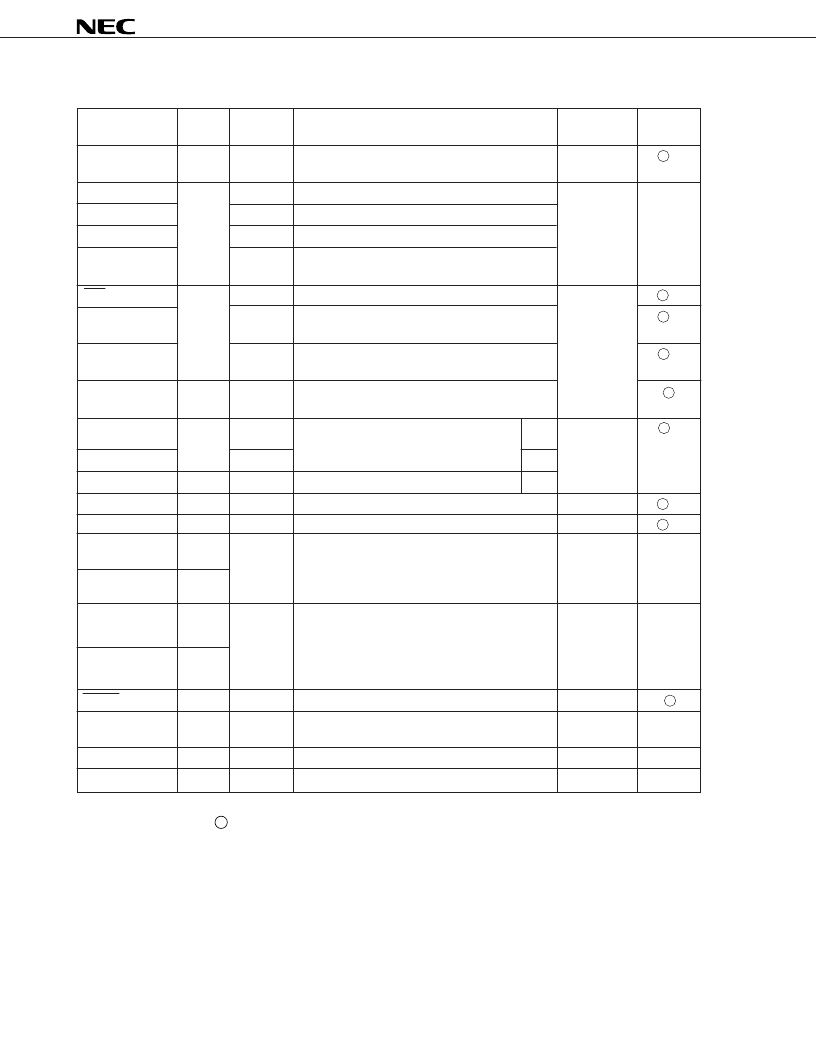

3.2 Non-Port Pins

Notes 1.

The circle (

2.

With a noise eliminator/asynchronously selectable

3.

Asynchronous

) indicates the Schmitt trigger input.

B

B

F

F

M

B

Function

Inputs external event pulse to the timer/event

counter

Timer/event counter output

Timer counter output

Clock output

Arbitrary frequency output (for buzzer output or

system clock trimming)

Serial clock I/O

Serial data output

Serial data bus I/O

Serial data input

Serial data bus I/O

Edge detection vectored interrupt input (both

rising and falling edges are detected)

Rising edge detection testable input

Falling edge detection testable input

Falling edge detection testable input

Pin for connecting a resistor (R) or capacitor (C)

for main system clock oscillation. An external

clock cannot be input.

Crystal connection pin for subsystem clock

generation. When external clock signal is used, it

is applied to XT1, and it reverse phase signal is

applied to XT2.

XT1 can be used as a 1-bit input (test).

System reset input (active low)

Internally connected. (To be connected directly to

V

DD

)

Positive power supply

Ground potential

Input/

output

Input

Output

I/O

Input

Input

Input

Input

Input

-

-

Input

-

Input

-

-

-

When reset

Input

Input

Input

Input

Input

Input

-

-

-

-

-

-

Edge detection vectored interrupt input

(detection edge selectable). A noise eliminator

can be selected when INT0/P10 is used.

Shared

pin

P13

P20

P21

P22

P23

P01

P02

P03

P00

P10

P11

P12

P60 - P63

P70 - P73

-

-

-

-

-

-

Note 3

Note 2

Note 3

I/O circuit

type

Note 1

-C

E-B

-A

-B

-C

-C

-A

F

-A

F

-

-

-

-

-

B

Pin name

TI0

PTO0

PTO1

PCL

BUZ

SCK

SO/SB0

SI/SB1

INT4

INT0

INT1

INT2

KR0 - KR3

KR4 - KR7

CL1

CL2

XT1

XT2

RESET

IC

V

DD

V

SS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD750106CUA | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| UPD750106GB | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| UPD750106GBA | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| UPD750108 | 4 BIT SINGLE-CHIP MICROCONTROLLER |

| UPD750108A | 4 BIT SINGLE-CHIP MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD7507C189 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD7508CU265 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD753012AGC-P33-8BT-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD753016AGC-P29-8BT | 制造商:Renesas Electronics Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。