- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376436 > UPD78324GJ (NEC Corp.) 16/8-BIT SINGLE-CHIP MICROCONTROLLER PDF資料下載

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁

12

μ

PD78323, 78324

RTP0 to RTP7

NMI

INTP0

INTP1

INTP2

INTP3

INTP4

INTP5

INTP6

TI

T

X

D

R

X

D

SO

SI

SB0

SB1

SCK

AD0 to AD7

1.2

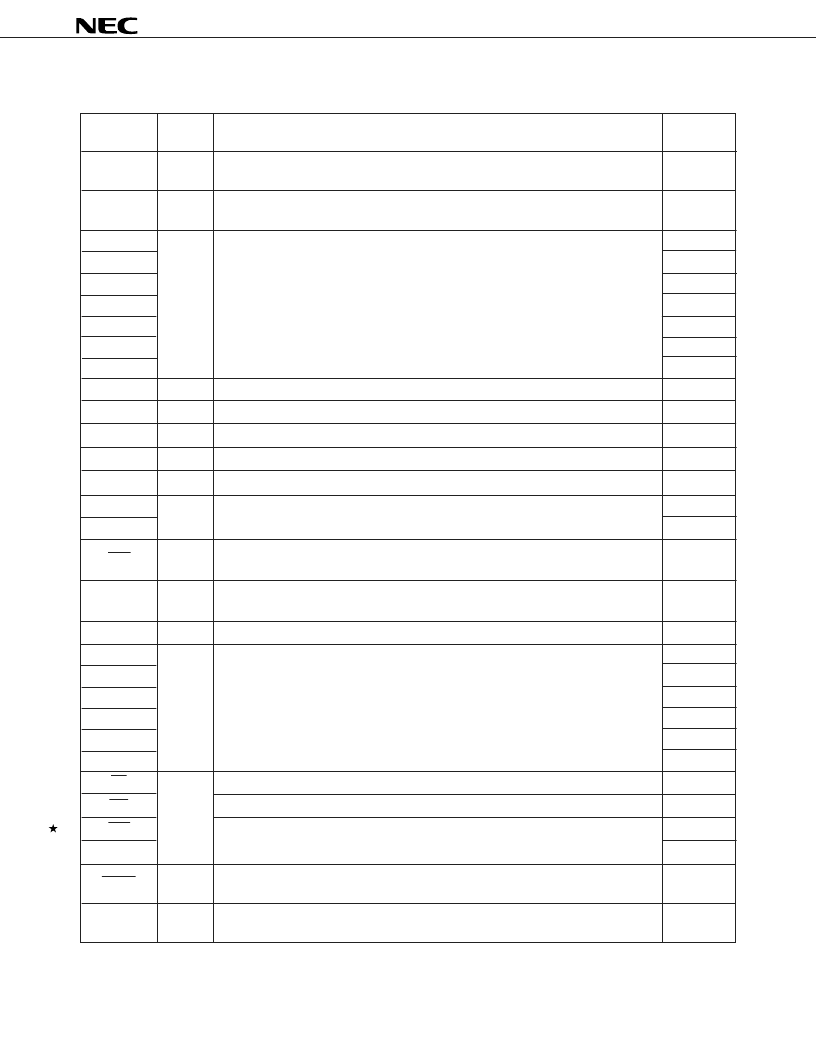

PINS OTHER THAN PORTS (1/2)

A8 to A15

TO00

TO01

TO02

TO03

TO10

TO11

RD

WR

TAS

TMD

WDTO

ASTB

Serial data output of asynchronous serial interface (UART)

Serial data input of asynchronous serial interface (UART)

Serial data output of clock synchronous serial interface in 3-wire mode

Serial data input of clock synchronous serial interface in 3-wire mode

Serial data output of clock synchronous serial interface in SBI mode

Dual-

Function Pin

Function

Pin Name

I/O

Realtime output port which generates pulses in synchronization with the trigger signal

transmitted from the realtime pulse unit (RPU).

Nonmaskable interrupot request input capable of specifying the effective at the rising or

falling edge by a mode register.

Input

Output

P00 to P07

P20

P21

P22

P23

P24

P25

P26

P27/TI

P27/INTP6

P30

P31

P32/SB0

P33/SB1

P32/SO

P33/SI

P34

P40 to P47

P50 to P57

P80

P81

P82

P83

P84

P85

P90

P91

P92

P93

––

––

Input

Input

External count clock input to timer 1 (TM1)

Output

Input

Output

Input

/output

Input

/output

Input

/output

Output

Output

Output

Strobe signal output generated for external memory read operation

Strobe signal output generated for external memory write operation

Control signal output generated for access to turbo access manager

μ

PD71P301

Note

Signal output indicating that the watchdog timer has generated a nonmascable

interrupt.

Timing signal output generated for externally latching the address information output from

pins AD0 to AD7 in order to access the external memory.

Output

Output

External interrupt request input capable of specifying the effective edgy by a mode

register.

Input

Serial clock input/output of clock synchronous serial interface

Multiplexed address/data bus for external memory expansion

Address bus for external memory expansion

Pulse output from the realtime pulse unit

Note

Maintenance product

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD78323 | 16/8-BIT SINGLE-CHIP MICROCONTROLLER |

| UPD78323LP | 16/8-BIT SINGLE-CHIP MICROCONTROLLER |

| UPD78324 | 16/8-BIT SINGLE-CHIP MICROCONTROLLER |

| UPD784217AY | 16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD784217AYGF | 16-BIT SINGLE-CHIP MICROCONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD78365AGF3B9 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| UPD784031GC-8BT-A | 制造商:Renesas Electronics Corporation 功能描述:MCU 8BIT/16BIT 78K4 CISC ROMLESS 3.3V/5V 80PQFP - Trays 制造商:Renesas Electronics 功能描述:16 制造商:Renesas Electronics 功能描述:16 Cut Tape |

| UPD784031GK-9EU-A | 制造商:Renesas Electronics Corporation 功能描述:16BIT K4 ROMLESS - Bulk |

| UPD784031YGC-8BT | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD784031YGC-8BT-A | 制造商:Renesas Electronics Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。