- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359318 > V370PDC (Electronic Theatre Controls, Inc.) High Performance PCI SDRAM Controller with Integrated Peripheral Control Unit PDF資料下載

參數(shù)資料

| 型號(hào): | V370PDC |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | High Performance PCI SDRAM Controller with Integrated Peripheral Control Unit |

| 中文描述: | 高性能PCI SDRAM控制器的集成了外圍控制單元 |

| 文件頁(yè)數(shù): | 3/14頁(yè) |

| 文件大?。?/td> | 99K |

| 代理商: | V370PDC |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

V370PDC

Copyright 1999, V3 Semiconductor Corp.

V370PDC_A0 Data Sheet Rev 1.01 DS-PD01-0101

3

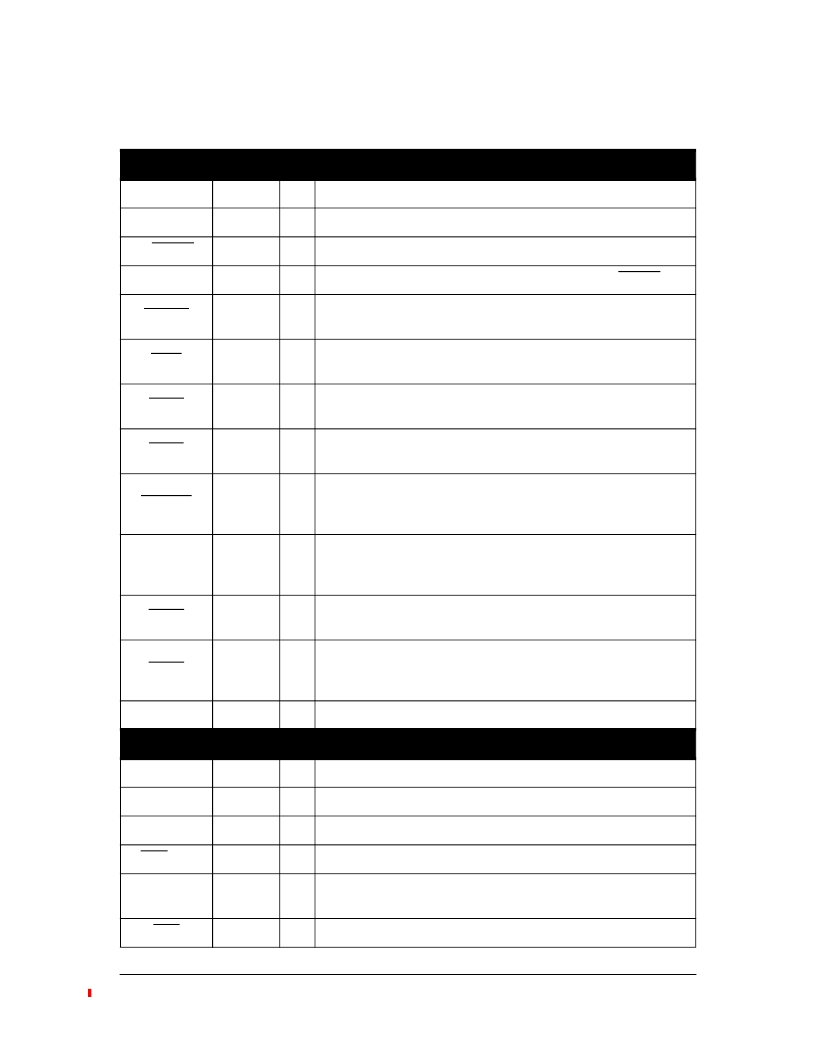

Table 3: Signal Descriptions

PCI Bus Interface

Signal

Type

R

a

Description

AD[31:0]

PCI I/O

Z

Address and data, multiplexed on the same pins.

C/BE[3:0]

PCI I

Bus Command and Byte Enables, multiplexed on the same pins.

PAR

PCI I/O

Z

Parity represents even parity across AD[31:0] and C/BE[3:0].

FRAME

PCI I

Cycle Frame indicates the beginning and burst length of an

access.

IRDY

PCI I

Initiator Ready indicates the initiating agent

’

s (bus master

’

s) ability

to complete the current data phase of the transaction.

TRDY

PCI O

Z

Target Ready indicates the target agent

’

s (selected device

’

s) abil-

ity to complete the current data phase of the transaction.

STOP

PCI O

Z

Stop indicates the current target is requesting the master to stop

the current transaction (retry or disconnect).

DEVSEL

PCI O

Z

Device Select, when actively driven by a target, indicates the driv-

ing device has decoded its address as the target of the current

access.

IDSEL

PCI I

Initialization Device Select is used as a chip select during configu-

ration read and write transactions. It must be driven high in order

to access the chip

’

s internal configuration space.

PERR

PCI I/O

Z

Parity Error is used to report data parity errors during all PCI

transactions except a Special Cycle.

SERR

PCI I/OD

Z

System Error is used to report address parity errors, data parity

errors on the Special Cycle command, or any other system error

where the result will be catastrophic.

PCLK

PCI I

PCLK provides timing for all transactions on the PCI bus.

SDRAM and Peripheral Bus Interface

Signal

Type

R

Description

CLKIN

I

Local clock input

CLKOUT

O

12

X

Buffered PCI clock output

DCS[3:0]

O

8

Z

SDRAM Chip Select

MA[14:0]

O

12

Z

SDRAM Memory Address (also, A[16:2] for peripheral access).

MA[14:13] are typically used for BA[1:0]

RAS

O

12

Z

SDRAM Row Address Strobe

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V375A12H150A | 375Vin / 24Vout / 150Watts DC-DC Converter Module |

| V375A12M200A | 375Vin / 5Vout / 200Watts DC-DC Converter Module |

| V375A12M300A | 375Vin / 24Vout / 300Watts DC-DC Converter Module |

| V375A12M500A | 48Vin / 12Vout / 500Watts DC-DC Converter Module |

| V375A24T600B | 375Vin / 24Vout / 600Watts DC-DC Converter Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V370PDC-66 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| V370PDC-66LP | 制造商:Rochester Electronics LLC 功能描述: 制造商:QuickLogic Corporation 功能描述: |

| V371 | 制造商:Varta 功能描述:Bulk |

| V3712PH | 制造商:Vishay Intertechnologies 功能描述: |

| V371AC | 制造商:Velleman Inc 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。