- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄140418 > W3E32M64S-200BI (MICROSEMI CORP-PMG MICROELECTRONICS) 32M X 64 DDR DRAM, 0.8 ns, PBGA219 PDF資料下載

參數(shù)資料

| 型號: | W3E32M64S-200BI |

| 廠商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分類: | DRAM |

| 英文描述: | 32M X 64 DDR DRAM, 0.8 ns, PBGA219 |

| 封裝: | 25 X 25 MM, PLASTIC, BGA-219 |

| 文件頁數(shù): | 16/17頁 |

| 文件大小: | 847K |

| 代理商: | W3E32M64S-200BI |

W3E32M64S-XBX

8

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

February 2007

Rev. 4

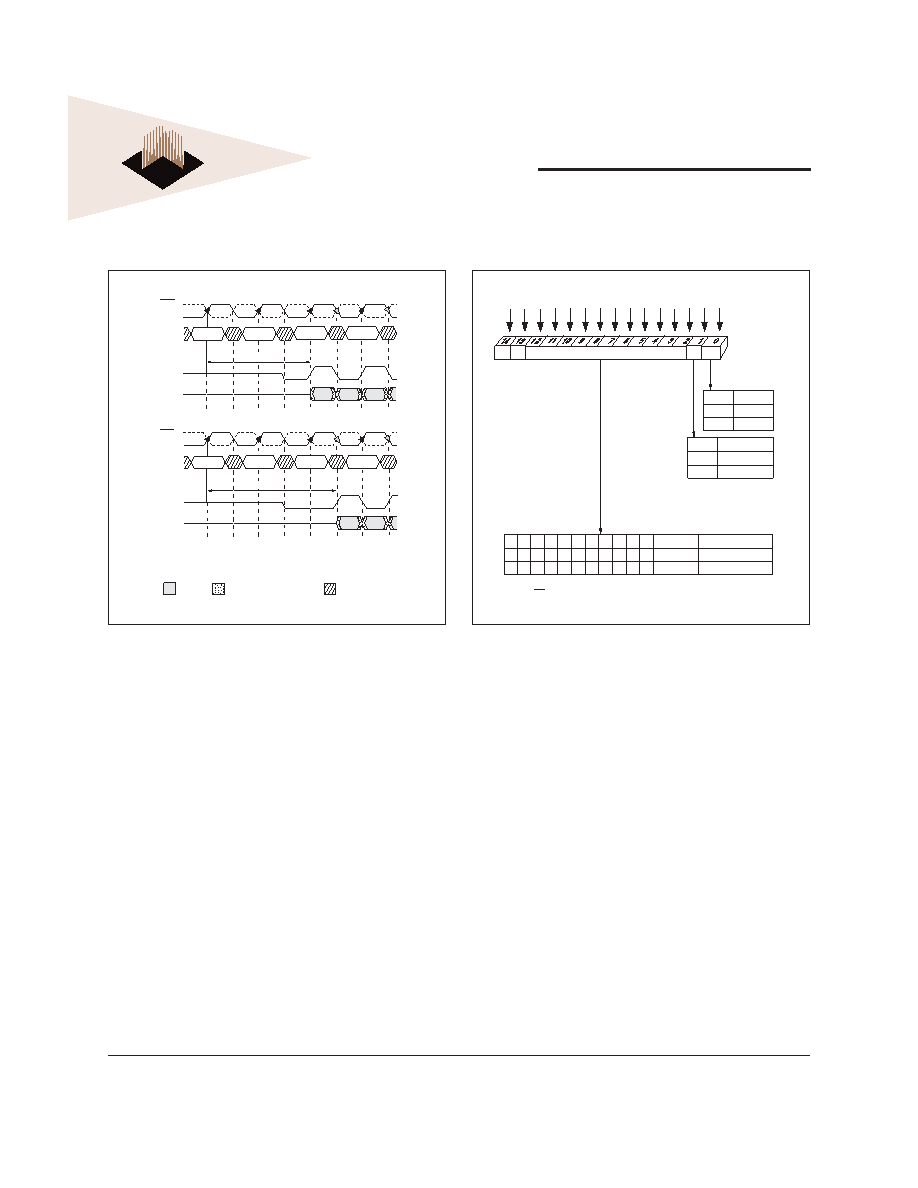

COMMAND

READ

NOP

CL = 2.5

DON'T CARE

TRANSITIONING DATA

DQ

DQS

T0

T1

T2

T2n

T3

T3n

COMMAND

READ

NOP

CL = 2

DQ

DQS

CLK

T0

T1

T2

T2n

T3

T3n

Burst Length = 4 in the cases shown

Shown with nominal tAC and nominal tDSDQ

DATA

CLK

FIGURE 4 – CAS LATENCY

FIGURE 5 – EXTENDED MODE

REGISTER DEFINITION

DLL

Enable

Disable

DLL

DS

A9

A7

A6

A5

A4

A3

A8

A2

A1

A0

Extended Mode

Register (Ex)

Address Bus

Operating Mode

A10

A11

11

01

BA0

BA1

E0

0

1

Drive Strength

Normal

Reduced

E1

0

1

Operating Mode

Reserved

E1, E0

Valid

-

E12

0

-

E10

0

-

E9

0

-

E8

0

-

E7

0

-

E6

0

-

E5

0

-

E4

0

-

E3

0

-

A12

E11

0

-

1. E14 and E13 must be "0, 1" to select the Extended Mode Register (vs. the base Mode Register)

2. The QFC function is not supported.

E2

0

-

allowed as long as it does not interrupt the data transfer

in the current bank and does not violate any other timing

parameters. Input A10 determines whether one or all

banks are to be precharged, and in the case where only

one bank is to be precharged, inputs BA0, BA1 select the

bank. Otherwise BA0, BA1 are treated as “Don’t Care.”

Once a bank has been precharged, it is in the idle state and

must be activated prior to any READ or WRITE commands

being issued to that bank. A PRECHARGE command will

be treated as a NOP if there is no open row in that bank

(idle state), or if the previously open row is already in the

process of precharging.

AUTO PRECHARGE

AUTO PRECHARGE is a feature which performs the

same individual-bank PRECHARGE function described

above, but without requiring an explicit command. This is

accomplished by using A10 to enable AUTO PRECHARGE

in conjunction with a specic READ or WRITE command.

A precharge of the bank/row that is addressed with the

READ or WRITE command is automatically performed

upon completion of the READ or WRITE burst. AUTO

PRECHARGE is non persistent in that it is either enabled

or disabled for each individual READ or WRITE command.

The device supports concurrent auto precharge if the

command to the other bank does not interrupt the data

transfer to the current bank.

AUTO PRECHARGE ensures that the precharge is

initiated at the earliest valid stage within a burst. This

“earliest valid stage” is determined as if an explicit

precharge command was issued at the earliest possible

time, without violating tRAS (MIN).The user must not issue

another command to the same bank until the precharge

time (tRP) is completed.

BURST TERMINATE

The BURST TERMINATE command is used to truncate

READ bursts (with auto precharge disabled). The most

recently registered READ command prior to the BURST

TERMINATE command will be truncated. The open page

which the READ burst was terminated from remains

open.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W3E32M64S-333BC | 32M X 64 DDR DRAM, 0.7 ns, PBGA219 |

| W3E64M72S-333BI | 64M X 72 SYNCHRONOUS DRAM, 0.7 ns, PBGA219 |

| W3HG2128M72AEF665F1MAG | 256M X 72 DDR DRAM MODULE, DMA240 |

| W7NCF02GH10CS3JG | 128M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF02GH10CS4HG | 128M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W3E32M64S-200BM | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 200 MHZ, 219 PBGA, MIL-TEMP. - Bulk |

| W3E32M64S-200SBC | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 200 MHZ, 208 PBGA, COMMERCIAL TEMP. - Bulk |

| W3E32M64S-200SBI | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 200 MHZ, 208 PBGA, INDUSTRIAL TEMP. - Bulk |

| W3E32M64S-200SBM | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 200 MHZ, 208 PBGA, MIL-TEMP. - Bulk |

| W3E32M64S-250BC | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 250 MHZ, 219 PBGA, COMMERCIAL TEMP. - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。