- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68457 > W3H128M72ER-667SBC (MICROSEMI CORP-PMG MICROELECTRONICS) 128M X 72 DDR DRAM, 0.5 ns, PBGA255 PDF資料下載

參數(shù)資料

| 型號: | W3H128M72ER-667SBC |

| 廠商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分類: | DRAM |

| 英文描述: | 128M X 72 DDR DRAM, 0.5 ns, PBGA255 |

| 封裝: | 23 X 21 MM, 1.27 MM PITCH, PLASTIC, BGA-255 |

| 文件頁數(shù): | 7/34頁 |

| 文件大?。?/td> | 1028K |

| 代理商: | W3H128M72ER-667SBC |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

W3H128M72ER-XNBX

15

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

February 2009

Rev. 6

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specications without notice.

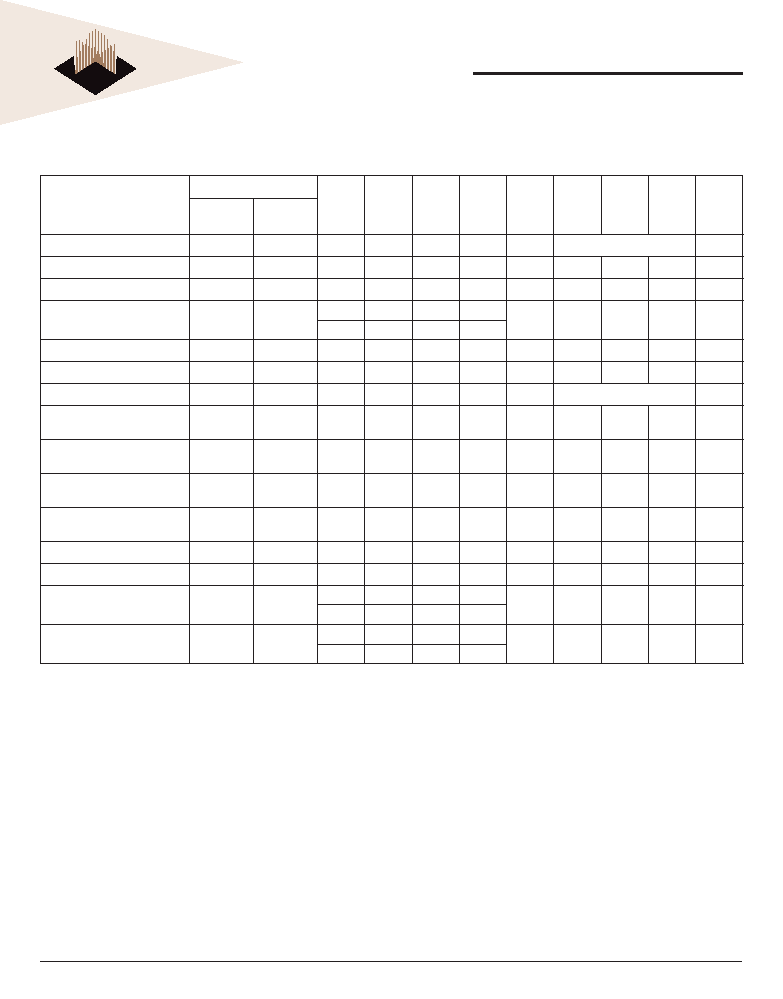

Function

CKE

CS#

RAS#

CAS#

WE#

BA2

BA1

BA0

A13

A12

A11

A10

A9-A0

Notes

Previous

Cycle

Current

Cycle

LOAD MODE

H

LLLL

BA

OP Code

2

REFRESH

H

L

H

XXXX

SELF-REFRESH Entry

H

L

H

XXXX

SELF-REFRESH Exit

LH

H

XXX

XXXX

7

L

HHH

Single bank precharge

HH

L

H

L

X

L

X

2

All banks PRECHARGE

HH

L

H

L

X

H

X

Bank activate

H

L

H

L

BA

Row Address

WRITE

HH

L

H

L

BA

Column

Address

L

Column

Address

2, 3

WRITE with auto precharge

HH

L

H

L

BA

Column

Address

H

Column

Address

2, 3

READ

H

LH

BA

Column

Address

L

Column

Address

2, 3

READ with auto precharge

H

LH

BA

Column

Address

H

Column

Address

2, 3

NO OPERATION

H

X

L

H

XXXX

Device DESELECT

H

X

H

XXXXXXX

POWER-DOWN entry

HL

H

XXX

XXXX

4

L

HHH

POWER-DOWN exit

LH

H

XXX

XXXX

4

L

HHH

Note: 1. All DDR2 SDRAM commands are dened by states of CS#, RAS#, CAS#, WE#, and CKE at the rising edge of the clock.

2. Bank addresses (BA) BA0–BA2 determine which bank is to be operated upon. BA during a LM command selects which mode register is programmed.

3. 3. Burst reads or writes at BL = 4 cannot be terminated or interrupted.

4. The power-down mode does not perform any REFRESH operations. The duration of power-down is therefore limited by the refresh requirements outlined in the AC

parametric section.

5. The state of ODT does not affect the states described in this table. The ODT function is not available during self refresh. See “On-Die Termination (ODT)” for details.

6. “X” means “H or L” (but a dened logic level).

7. Self refresh exit is asynchronous.

TABLE 3 – TRUTH TABLE - DDR2 COMMANDS

Notes 1, 5, and 6 apply to all

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W3H128M72ER2-400SBI | 128M X 72 DDR DRAM, 0.6 ns, PBGA255 |

| W3H32M64E-400SBM | 32M X 64 DDR DRAM, 0.6 ns, PBGA208 |

| W3H32M64E-667SBC | 32M X 64 DDR DRAM, 0.65 ns, PBGA208 |

| W3H32M64EA-400SBC | 32M X 64 DDR DRAM, PBGA208 |

| W3H32M64EA-667SBM | 32M X 64 DDR DRAM, PBGA208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W3H13C1048AT | 制造商:AVX 制造商全稱:AVX Corporation 功能描述:High Current Feedthry Capacitors |

| W3H13C1048AT1A | 功能描述:饋通電容器 25volt 0.1uF X7R RoHS:否 制造商:Tusonix 電容:8200 pF 容差:- 20 %, + 80 % 電壓額定值: 工作溫度范圍: 溫度系數(shù): 封裝 / 箱體: |

| W3H13C1048AT1F | 功能描述:饋通電容器 25volt 0.1uF X7R RoHS:否 制造商:Tusonix 電容:8200 pF 容差:- 20 %, + 80 % 電壓額定值: 工作溫度范圍: 溫度系數(shù): 封裝 / 箱體: |

| W3H15C1038AT | 制造商:AVX 制造商全稱:AVX Corporation 功能描述:High Current Feedthry Capacitors |

| W3H15C1038AT1A | 功能描述:饋通電容器 50volt .01uF X7R RoHS:否 制造商:Tusonix 電容:8200 pF 容差:- 20 %, + 80 % 電壓額定值: 工作溫度范圍: 溫度系數(shù): 封裝 / 箱體: |

發(fā)布緊急采購,3分鐘左右您將得到回復。