- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄245679 > W3H64M72E-400SBM (WHITE ELECTRONIC DESIGNS CORP) 64M X 72 DDR DRAM, 0.6 ns, PBGA208 PDF資料下載

參數(shù)資料

| 型號(hào): | W3H64M72E-400SBM |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | DRAM |

| 英文描述: | 64M X 72 DDR DRAM, 0.6 ns, PBGA208 |

| 封裝: | 16 X 22 MM, 1 MM PITCH, PLASTIC, BGA-208 |

| 文件頁(yè)數(shù): | 7/32頁(yè) |

| 文件大小: | 944K |

| 代理商: | W3H64M72E-400SBM |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

W3H64M72E-XSBX

W3H64M72E-XSBXF

15

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

December 2009

2010 White Electronic Designs Corp. All rights reserved

Rev. 9

White Electronic Designs Corp. reserves the right to change products or specications without notice.

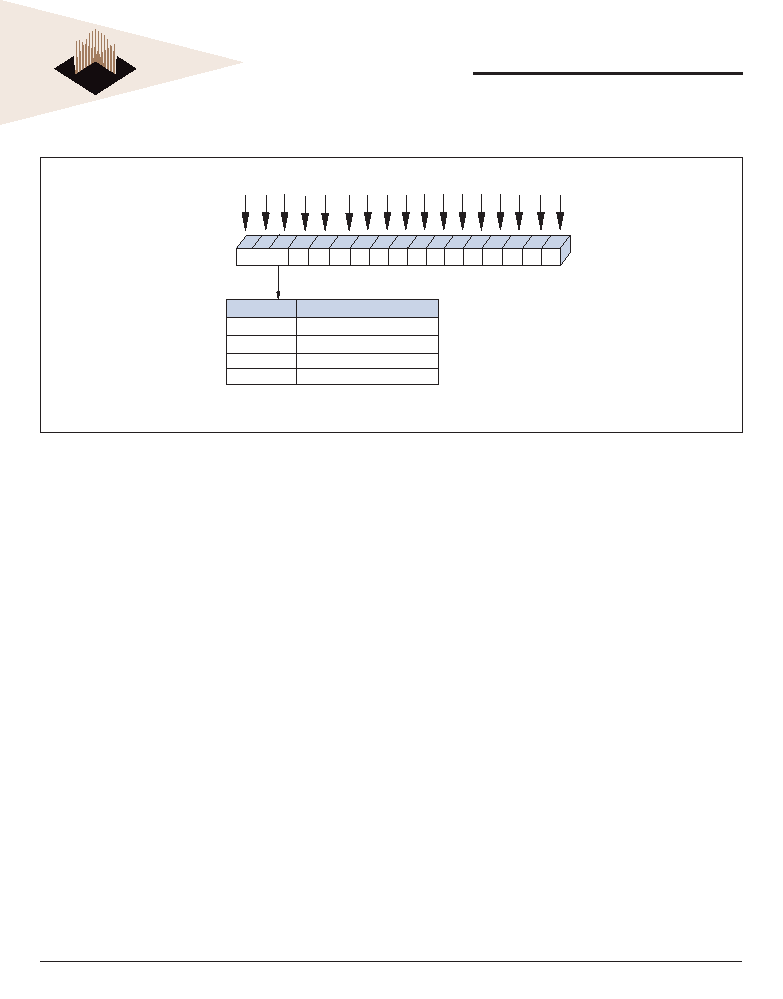

EXTENDED MODE REGISTER 2

The extended mode register 2 (EMR2) controls functions

beyond those controlled by the mode register. Currently

all bits in EMR2 are reserved, as shown in Figure 8. The

EMR2 is programmed via the LM command and will

retain the stored information until it is programmed again

or the device loses power. Reprogramming the EMR will

not alter the contents of the memory array, provided it is

performed correctly.

Bit E7 (A7) must be programmed as"1" to provide a faster

refresh rate on devices if the TCASE exceeds 85°C

EMR2 must be loaded when all banks are idle and no

bursts are in progress, and the controller must wait the

specied time tMRD before initiating any subsequent

operation. Violating either of these requirements could

result in unspecied operation.

EXTENDED MODE REGISTER 3

The extended mode register 3 (EMR3) controls functions

beyond those controlled by the mode register. Currently,

all bits in EMR3 are reserved, as shown in Figure 9.

The EMR3 is programmed via the LM command and will

retain the stored information until it is programmed again

or the device loses power. Reprogramming the EMR will

not alter the contents of the memory array, provided it is

performed correctly.

EMR3 must be loaded when all banks are idle and no

bursts are in progress, and the controller must wait the

specied time tMRD before initiating any subsequent

operation. Violating either of these requirements could

result in unspecied operation.

COMMAND TRUTH TABLES

The following tables provide a quick reference of DDR2

SDRAM available commands, including CKE power-down

modes, and bank-to-bank commands.

FIGURE 9 – EXTENDED MODE REGISTER 3 (EMR3) DEFINITION

A9

A7 A 6 A5 A4 A3

A8

A2

A1 A0

Exten ded Mo de

Re gister (Ex)

Address Bus

97

6

5

4

3

82

1

0

A10

A12 A11

BA0

BA1

10

11

12

13

14

15

A13

0

1

0

1

Mode Register Definition

M15

0

0

1

M14

EMR3

01

BA2

16

M1 6

0

0

Mode register (MR)

Extended mode register (EMR)

Extended mode register (EMR2)

Extended mode register (EMR3)

Note: 1. E13 (A13)-E0 (A0) are reserved for future use and must be programmed to

"0." A13 is not used in this device.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| WS128K32-70G4QE | 512K X 8 MULTI DEVICE SRAM MODULE, 70 ns, CQFP68 |

| WS128K32-85G4ME | 512K X 8 MULTI DEVICE SRAM MODULE, 85 ns, CQFP68 |

| WMS128K8L-25FI | 128K X 8 STANDARD SRAM, 25 ns, CDFP36 |

| WMS128K8L-55DEI | 128K X 8 STANDARD SRAM, 55 ns, CDSO32 |

| WMS128K8L-55DEMA | 128K X 8 STANDARD SRAM, 55 ns, CDSO32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W3H64M72E-533ES | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:64M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H64M72E-533ESC | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:64M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H64M72E-533ESI | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:64M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H64M72E-533ESM | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:64M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H64M72E-533SB | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:64M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。