- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361798 > W981204AH-8H x4 SDRAM PDF資料下載

參數(shù)資料

| 型號: | W981204AH-8H |

| 英文描述: | x4 SDRAM |

| 中文描述: | x4內(nèi)存 |

| 文件頁數(shù): | 6/42頁 |

| 文件大?。?/td> | 1082K |

| 代理商: | W981204AH-8H |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

W981204AH

8M x 4 Banks x 4 bits SDRAM

Revision 1.0 Publication Release Date: June, 2000

- 6 -

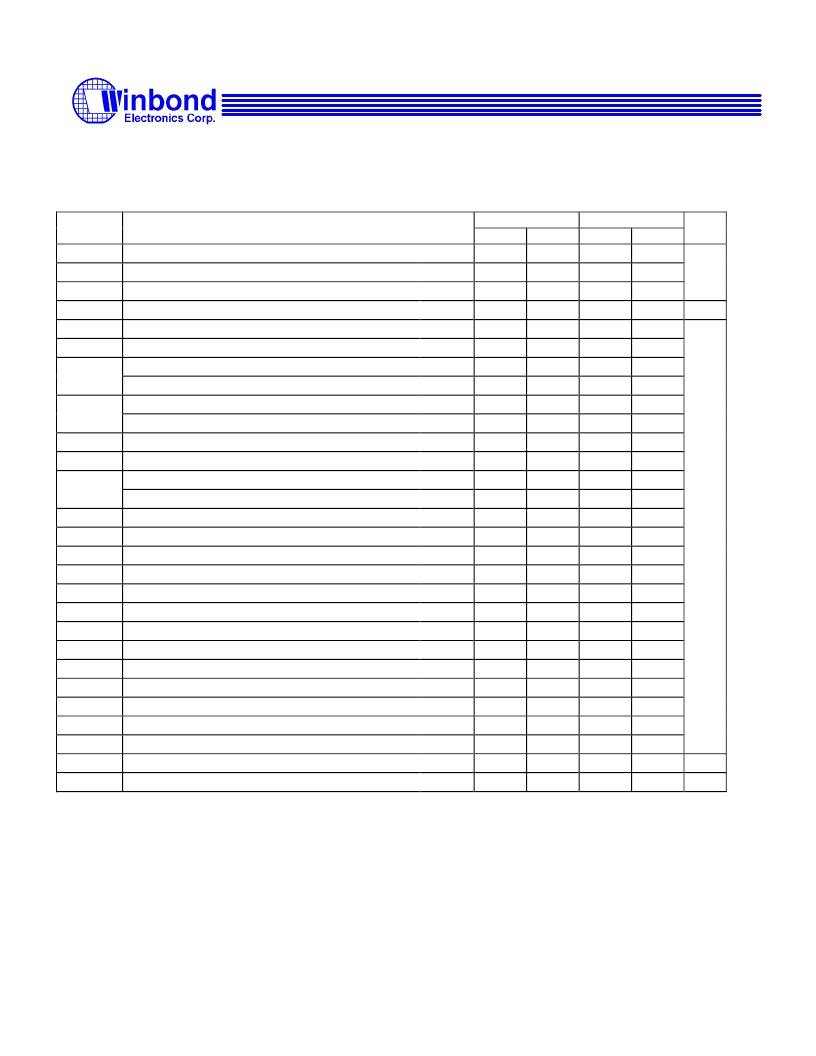

AC CHARACTERISTICS AND OPERATING CONDITION

(Vcc=3.3V

±

0.3V, Ta=0

°

to 70

°

C Notes: 5, 6, 7, 8)

-75 (PC133)

MIN

-8H (PC100)

MIN

SYMBOL

PARAMETER

MAX

MAX

UNIT

t

RC

Ref/Active to Ref/Active Command Period

65

68

t

RAS

Active to precharge Command Period

45

100000

48

100000

ns

t

RCD

Active to Read/Write Command Delay Time

20

20

t

CCD

Read/Write(a) to Read/Write(b)Command Period

1

1

cycle

t

RP

Precharge to Active Command Period

20

20

t

RRD

Active(a) to Active(b) Command Period

15

20

t

WR

Write Recovery Time

CL*=2

10

10

CL*=3

7.5

8

t

CK

CLK Cycle Time

CL*=2

10

1000

10

1000

CL*=3

7.5

1000

8

1000

t

CH

CLK High Level width

2.5

3

t

CL

CLK Low Level width

2.5

3

t

AC

Access Time from CLK

CL*=2

6

6

CL*=3

5.4

6

ns

t

OH

Output Data Hold Time

2.7

3

t

HZ

Output Data High Impedance Time

2.7

7.5

3

8

t

LZ

Output Data Low Impedance Time

0

0

t

SB

Power Down Mode Entry Time

0

7.5

0

8

t

T

Transition Time of CLK (Rise and Fall)

0.5

10

0.5

10

t

DS

Data-in Set-up Time

1.5

2

t

DH

Data-in Hold Time

0.8

1

t

AS

Address Set-up Time

1.5

2

t

AH

Address Hold Time

0.8

1

t

CKS

CKE Set-up Time

1.5

2

t

CKH

CKE Hold Time

0.8

1

t

CMS

Command Set-up Time

1.5

2

t

CMH

Command Hold Time

0.8

1

t

REF

Refresh Time

64

64

ms

t

RSC

Mode register Set Cycle Time

15

16

ns

*CL=CAS Latency

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W982504AH-7 | x4 SDRAM |

| W982504AH-75 | x4 SDRAM |

| W982504AH-8H | x4 SDRAM |

| W982508AH-7 | x8 SDRAM |

| W982508AH-75 | x8 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W981208AH | 制造商:WINBOND 制造商全稱:Winbond 功能描述:4M x 8 bit x 4 Banks SDRAM |

| W981208AH-75 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:x8 SDRAM |

| W981208AH-8H | 制造商:WINBOND 制造商全稱:Winbond 功能描述:x8 SDRAM |

| W981208BH | 制造商:WINBOND 制造商全稱:Winbond 功能描述:4M x 4 BANKS x 8 BIT SDRAM |

| W981208BH-7 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:x8 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。