- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202124 > WE32K32N-80H1CA (WHITE ELECTRONIC DESIGNS CORP) 32K X 32 EEPROM 5V MODULE, 80 ns, CPGA66 PDF資料下載

參數(shù)資料

| 型號(hào): | WE32K32N-80H1CA |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | PROM |

| 英文描述: | 32K X 32 EEPROM 5V MODULE, 80 ns, CPGA66 |

| 封裝: | 1.075 X 1.075 INCH, HERMETIC SEALED, CERAMIC, HIP-66 |

| 文件頁(yè)數(shù): | 2/13頁(yè) |

| 文件大小: | 533K |

| 代理商: | WE32K32N-80H1CA |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)

10

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

WE32K32-XXX

March 2006

Rev. 4

White Electronic Designs Corp. reserves the right to change products or specications without notice.

SOFTWARE DATA PROTECTION

A software write protection feature may be enabled

or disabled by the user. When shipped by White

Microelectronics, the WE32K32-XXX has the feature

disabled. Write access to the device is unrestricted.

To enable software write protection, the user writes three

access code bytes to three special internal locations.

Once write protection has been enabled, each write to the

EEPROM must use the same three byte write sequence

to permit writing. After setting software data protection,

any attempt to write to the device without the three-byte

command sequence will start the internal write timers. No

data will be written to the device, however, for the duration

of tWC. The write protection feature can be disabled by

a six byte write sequence of specic data to specic

locations. Power transitions will not reset the software

write protection.

Each 32KByte block of the EEPROM has independent write

protection. One or more blocks may be enabled and the rest

disabled in any combination. The software write protection

guards against inadvertent writes during power transitions,

or unauthorized modication using a PROM programmer.

HARDWARE DATA PROTECTION

These features protect against inadvertent writes to the

WE32K32-XXX. These are included to improve reliability

during normal operation:

a)

VCC power on delay

As VCC climbs past 3.8V typical the device will wait

5msec typical before allowing write cycles.

b)

VCC sense

While below 3.8V typical write cycles are inhibited.

c)

Write inhibiting

Holding OE# low and either CS# or WE# high

inhibits write cycles.

d)

Noise lter

Pulses of <8ns (typ) on WE# or CS# will not initiate

a write cycle.

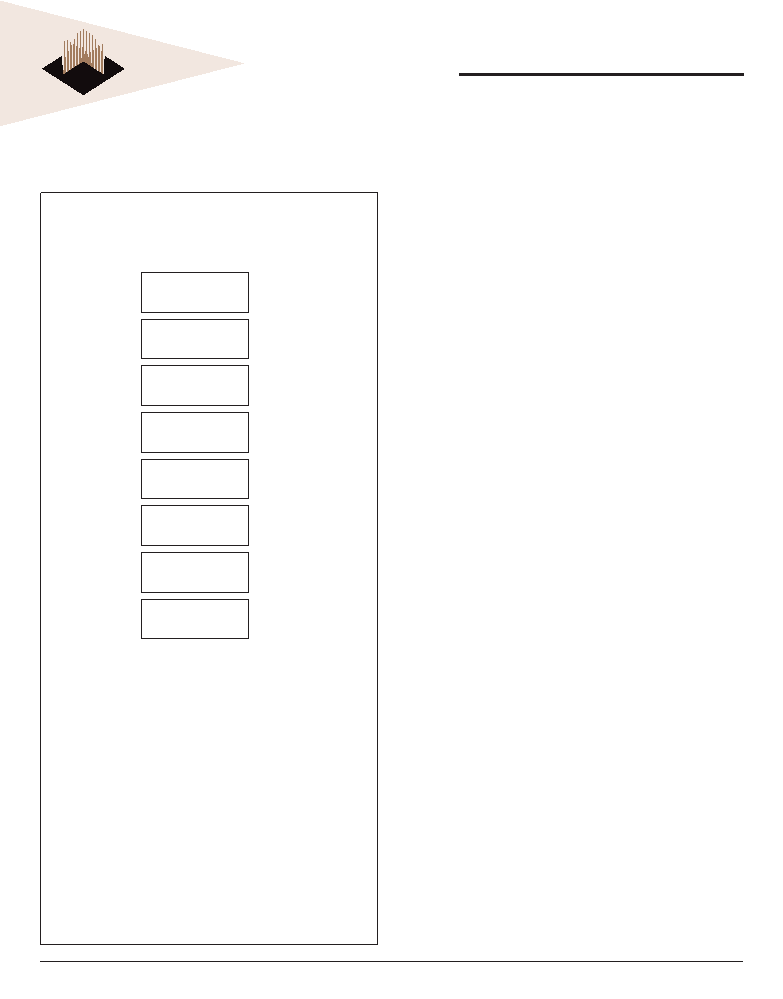

LOAD DATA AA

TO

ADDRESS 5555

LOAD DATA 55

TO

ADDRESS 2AAA

LOAD DATA 80

TO

ADDRESS 5555

LOAD DATA AA

TO

ADDRESS 5555

LOAD DATA 55

TO

ADDRESS 2AAA

LOAD DATA 20

TO

ADDRESS 5555

LOAD DATA XX

TO

ANY ADDRESS(4)

LOAD LAST BYTE

TO

LAST ADDRESS

FIGURE 10 –

SOFTWARE BLOCK DATA PROTECTION

DISABLE ALGORITHM(1)

NOTES:

1. Data Format: I/O15-0 (Hex);

Address Format: A16 -A0 (Hex).

2. Write Protect state will be activated at end of write even if no other

data is loaded.

3. Write Protect state will be deactivated at end of write period even if

no other data is loaded.

4. 1 to 64 bytes of data may loaded.

EXIT DATA

PROTECT STATE(3)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| WE32K32N-120H1IA | 32K X 32 EEPROM 5V MODULE, 120 ns, CPGA66 |

| WS512K32N-17H2MA | 2M X 8 MULTI DEVICE SRAM MODULE, 17 ns, CPGA66 |

| WS512K32N-25H2M | 2M X 8 MULTI DEVICE SRAM MODULE, 25 ns, CPGA66 |

| WME128K8-150CQ | 128K X 8 EEPROM 5V, 150 ns, CDIP32 |

| WMS256K16-20FGC | 256K X 16 STANDARD SRAM, 20 ns, CDSO44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| WE32K32N-80H1I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| WE32K32N-80H1IA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| WE32K32N-80H1M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| WE32K32N-80H1MA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| WE32K32N-80H1Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。