- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371303 > X9448WV24-2.7 (Intersil Corporation) Mixed Signal with 2-Wire Interface PDF資料下載

參數(shù)資料

| 型號(hào): | X9448WV24-2.7 |

| 廠商: | Intersil Corporation |

| 英文描述: | Mixed Signal with 2-Wire Interface |

| 中文描述: | 混合信號(hào)的2線接口 |

| 文件頁數(shù): | 3/20頁 |

| 文件大小: | 127K |

| 代理商: | X9448WV24-2.7 |

X9448

Characteristics subject to change without notice.

3 of 20

REV 1.0 6/21/00

www.xicor.com

PIN NAMES

PRINCIPLES OF OPERATION

The X9448 is a highly integrated microcircuit incorpo-

rating two resistor arrays, two voltage comparators

and their associated registers and counters; and the

serial interface logic providing direct communication

between the host and the digitally-controlled potenti-

ometers and voltage comparators.

Serial Interface

The X9448 supports a bidirectional bus oriented proto-

col. The protocol defines any device that sends data

onto the bus as a transmitter and the receiving device

as the receiver. The device controlling the transfer is a

master and the device being controlled is the slave.

The master will always initiate data transfers and pro-

vide the clock for both transmit and receive operations.

Therefore, the X9448 will be considered a slave device

in all applications.

Clock and Data Conventions

Data states on the SDA line can change only during

SCL LOW periods (t

LOW

). SDA state changes during

SCL HIGH are reserved for indicating start and stop

conditions.

Start Condition

All commands to the X9448 are preceded by the start

condition, which is a HIGH to LOW transition of SDA

while SCL is HIGH (t

HIGH

). The X9448 continuously

monitors the SDA and SCL lines for the start condition

and will not respond to any command until this condi-

tion is met.

Stop Condition

All communications must be terminated by a stop con-

dition, which is a LOW to HIGH transition of SDA while

SCL is HIGH.

Acknowledge

Acknowledge is a software convention used to provide

a positive handshake between the master and slave

devices on the bus to indicate the successful receipt of

data. The transmitting device, either the master or the

slave, will release the SDA bus after transmitting eight

bits. The master generates a ninth clock cycle and dur-

ing this period the receiver pulls the SDA line LOW to

acknowledge that it successfully received the eight bits

of data.

The X9448 will respond with an acknowledge after

recognition of a start condition and its slave address

and once again after successful receipt of the com-

mand byte. If the command is followed by a data byte

the X9448 will respond with a final acknowledge.

Array Description

The X9448 is comprised of two resistor arrays and two

voltage comparators. Each array contains 63 discrete

resistive segments that are connected in series. The

physical ends of each array are equivalent to the fixed

terminals of a mechanical potentiometer (V

inputs).

H

and V

L

At both ends of each array and between each resistor

segment is a CMOS switch connected to the wiper

(V

W

) output. Within each individual array only one

switch may be turned on at a time. These switches are

controlled by a volatile wiper counter register (WCR).

The six bits of the WCR are decoded to select, and

enable, one of sixty-four switches.

The WCR may be written directly, or it can be changed

by transferring the contents of one of four associated

data registers into the WCR. These data registers and

the WCR can be read and written by the host system.

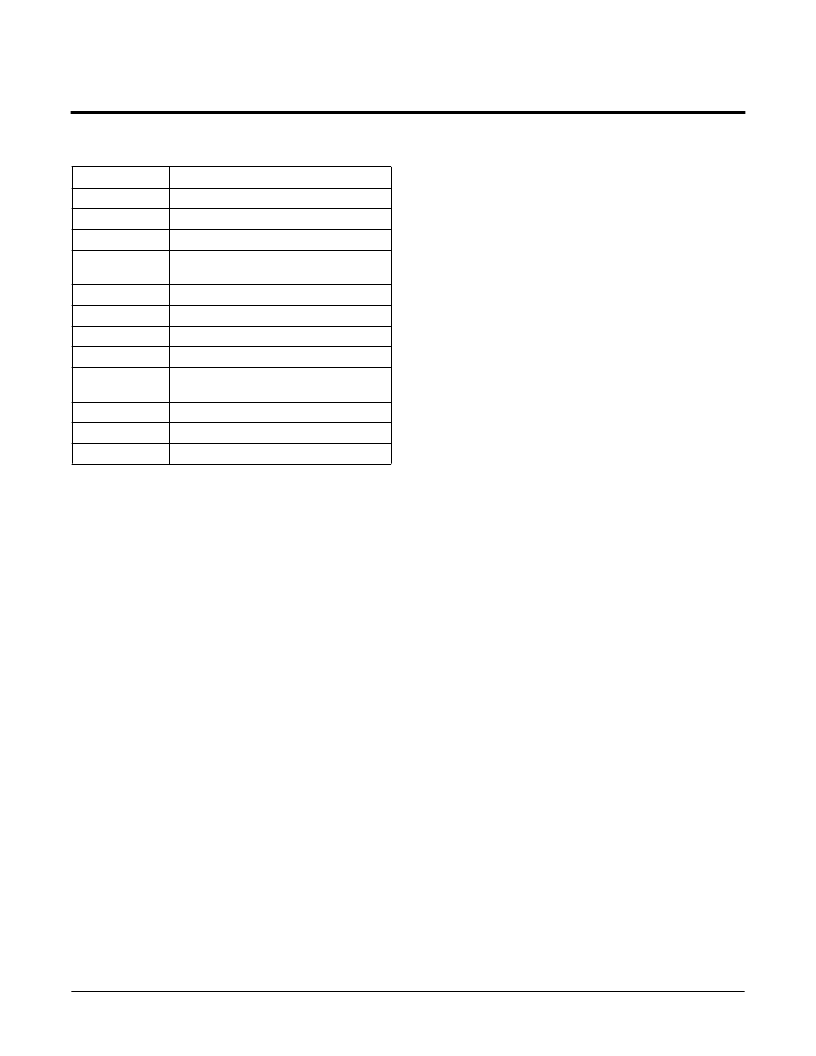

Symbol

SCL

SDA

A0-A3

V

H0

–V

V

L0

–V

V

W0

–V

V

NI0

, V

V

OUT0,

WP

V+,V-

Description

Serial Clock

Serial Data

Device Address

Potentiometers (terminal equivalent)

H1

L1

,

W1

Potentiometers (wiper equivalent)

Comparator Input Voltages

Buffered Comparator Outputs

Hardware Write Protection

Analog and Voltage Comparator

Supplies

System/Digital Supply Voltage

System Ground

No Connection

NI1

V

OUT1

V

V

NC

CC

SS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X9448WV24I | Mixed Signal with 2-Wire Interface |

| X9448YV24I | Mixed Signal with 2-Wire Interface |

| X9448YV24I-2.7 | Mixed Signal with 2-Wire Interface |

| X9448YS24I-2.7 | Mixed Signal with 2-Wire Interface |

| X9448 | Mixed Signal with 2-Wire Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X9448WV24I | 功能描述:IC DUAL PROG COMP 10K 24TSSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 數(shù)字電位器 系列:XDCP™ 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 接片:256 電阻(歐姆):100k 電路數(shù):1 溫度系數(shù):標(biāo)準(zhǔn)值 35 ppm/°C 存儲(chǔ)器類型:非易失 接口:3 線串口 電源電壓:2.7 V ~ 5.25 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:8-WDFN 裸露焊盤 供應(yīng)商設(shè)備封裝:8-TDFN-EP(3x3) 包裝:剪切帶 (CT) 產(chǎn)品目錄頁面:1399 (CN2011-ZH PDF) 其它名稱:MAX5423ETA+TCT |

| X9448WV24I-2.7 | 功能描述:IC DUAL PROG COMP 10K 24TSSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 數(shù)字電位器 系列:XDCP™ 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 接片:256 電阻(歐姆):100k 電路數(shù):1 溫度系數(shù):標(biāo)準(zhǔn)值 35 ppm/°C 存儲(chǔ)器類型:非易失 接口:3 線串口 電源電壓:2.7 V ~ 5.25 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:8-WDFN 裸露焊盤 供應(yīng)商設(shè)備封裝:8-TDFN-EP(3x3) 包裝:剪切帶 (CT) 產(chǎn)品目錄頁面:1399 (CN2011-ZH PDF) 其它名稱:MAX5423ETA+TCT |

| X9448YP24 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Mixed Signal with 2-Wire Interface |

| X9448YP24-2.7 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Mixed Signal with 2-Wire Interface |

| X9448YP24I | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Mixed Signal with 2-Wire Interface |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。