- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4282 > XA3S500E-4CPG132Q (Xilinx Inc)IC FPGA SPARTAN-3E 500K 132CSBGA PDF資料下載

參數(shù)資料

| 型號: | XA3S500E-4CPG132Q |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 19/37頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN-3E 500K 132CSBGA |

| 標(biāo)準(zhǔn)包裝: | 360 |

| 系列: | Spartan®-3E XA |

| LAB/CLB數(shù): | 1164 |

| 邏輯元件/單元數(shù): | 10476 |

| RAM 位總計: | 368640 |

| 輸入/輸出數(shù): | 92 |

| 門數(shù): | 500000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 125°C |

| 封裝/外殼: | 132-TFBGA,CSPBGA |

| 供應(yīng)商設(shè)備封裝: | 132-CSPBGA(8x8) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

DS635 (v2.0) September 9, 2009

Product Specification

26

R

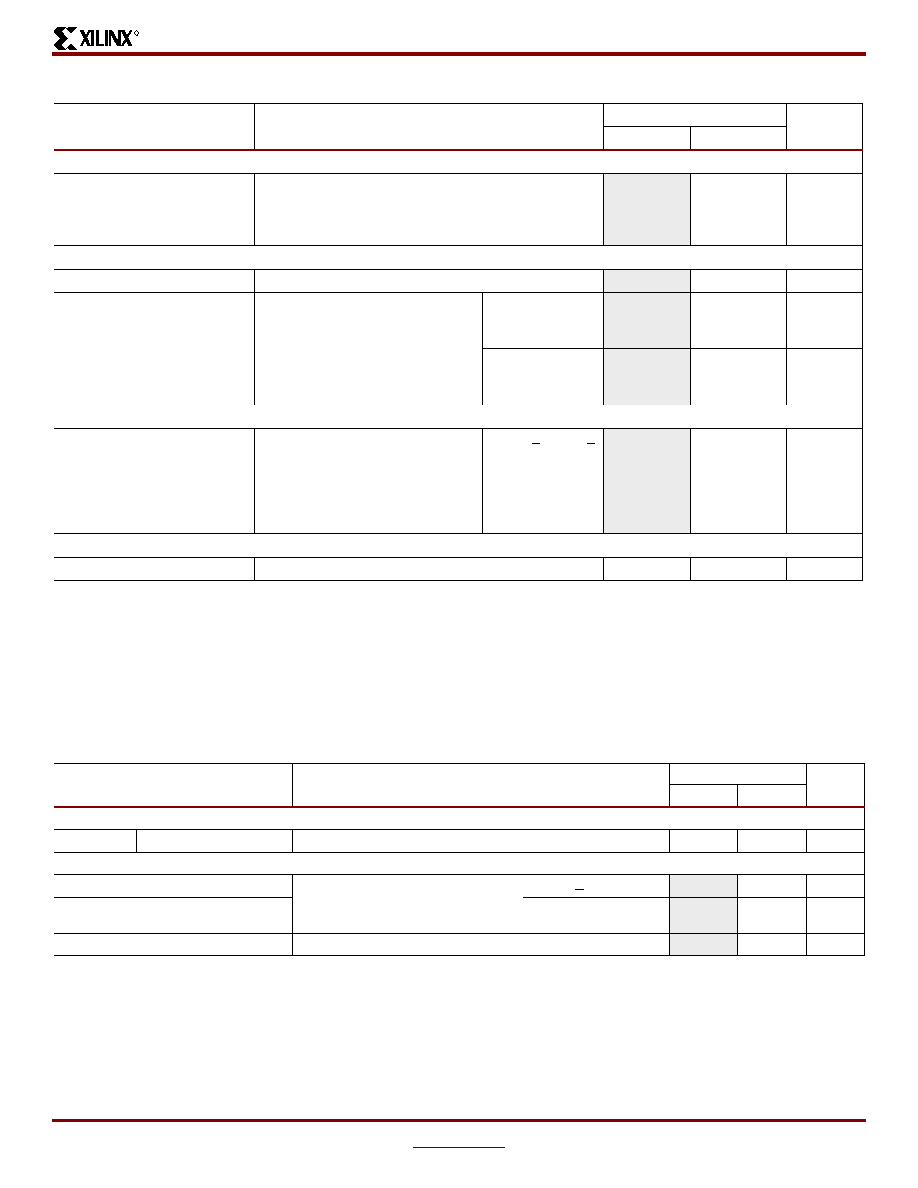

Digital Frequency Synthesizer

Duty Cycle(4)

CLKOUT_DUTY_CYCLE_DLL

Duty cycle variation for the CLK0, CLK90, CLK180,

CLK270, CLK2X, CLK2X180, and CLKDV outputs,

including the BUFGMUX and clock tree duty-cycle

distortion

-±[1% of

CLKIN period

+ 400]

ps

Phase Alignment(4)

CLKIN_CLKFB_PHASE

Phase offset between the CLKIN and CLKFB inputs

-

±200

ps

CLKOUT_PHASE_DLL

Phase offset between DLL outputs

CLK0 to CLK2X

(not CLK2X180)

-±[1% of

CLKIN period

+ 100]

ps

All others

-±[1% of

CLKIN period

+ 200]

ps

Lock Time

LOCK_DLL(3)

When using the DLL alone: The time

from deassertion at the DCM’s Reset

input to the rising transition at its

LOCKED output. When the DCM is

locked, the CLKIN and CLKFB

signals are in phase

5 MHz < FCLKIN <

15 MHz

-5

ms

FCLKIN > 15 MHz

-

600

μs

Delay Lines

DCM_DELAY_STEP

Finest delay resolution

20

40

ps

Notes:

1.

2.

Indicates the maximum amount of output jitter that the DCM adds to the jitter on the CLKIN input.

3.

For optimal jitter tolerance and faster lock time, use the CLKIN_PERIOD attribute.

4.

Some jitter and duty-cycle specifications include 1% of input clock period or 0.01 UI. Example: The data sheet specifies a maximum

jitter of “±[1% of CLKIN period + 150]”. Assume the CLKIN frequency is 100 MHz. The equivalent CLKIN period is 10 ns and 1% of

10 ns is 0.1 ns or 100 ps. According to the data sheet, the maximum jitter is ±[100 ps + 150 ps] = ±250ps.

Table 27: Switching Characteristics for the DLL (Continued)

Symbol

Description

-4 Speed Grade

Units

Min

Max

Table 28: Recommended Operating Conditions for the DFS

Symbol

Description

-4 Speed Grade

Units

Min

Max

Input Frequency Ranges(2)

FCLKIN

CLKIN_FREQ_FX

Frequency for the CLKIN input

0.200

333(4)

MHz

Input Clock Jitter Tolerance(3)

CLKIN_CYC_JITT_FX_LF

Cycle-to-cycle jitter at the CLKIN

input, based on CLKFX output

frequency

FCLKFX < 150 MHz

-±300

ps

CLKIN_CYC_JITT_FX_HF

FCLKFX > 150 MHz

-±150

ps

CLKIN_PER_JITT_FX

Period jitter at the CLKIN input

-±1

ns

Notes:

1.

DFS specifications apply when either of the DFS outputs (CLKFX or CLKFX180) are used.

2.

If both DFS and DLL outputs are used on the same DCM, follow the more restrictive CLKIN_FREQ_DLL specifications in Table 26.

3.

CLKIN input jitter beyond these limits may cause the DCM to lose lock.

4.

To support double the maximum effective FCLKIN limit, set the CLKIN_DIVIDE_BY_2 attribute to TRUE. This attribute divides the incoming

clock frequency by two as it enters the DCM.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 828101-1 | CONN D-SUB FEMALE SCREW LOCK |

| AMM31DRSN-S288 | CONN EDGECARD 62POS .156 EXTEND |

| AMM31DRSH-S288 | CONN EDGECARD 62POS .156 EXTEND |

| XC6SLX16-L1CSG324C | IC FPGA SPARTAN 6 14K 324CSGBGA |

| AMM31DRSD-S288 | CONN EDGECARD 62POS .156 EXTEND |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XA3S500E-4FT256Q | 功能描述:IC FPGA SPARTAN-3E 256FPBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4FTG256I | 功能描述:IC FPGA SPARTAN-3E 500K 256FTBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4FTG256Q | 功能描述:IC FPGA SPARTAN-3E 500K 256FTBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4PQG208I | 功能描述:IC FPGA SPARTAN-3E 500K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4PQG208Q | 功能描述:IC FPGA SPARTAN-3E 500K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。