- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19907 > XC18V01PCG20C (Xilinx Inc)IC PROM SERIAL CONFIG 1M 20-PLCC PDF資料下載

參數(shù)資料

| 型號: | XC18V01PCG20C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 16/24頁 |

| 文件大小: | 0K |

| 描述: | IC PROM SERIAL CONFIG 1M 20-PLCC |

| 標準包裝: | 46 |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 存儲容量: | 1Mb |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 20-LCC(J 形引線) |

| 供應商設備封裝: | 20-PLCC |

| 包裝: | 管件 |

| 產(chǎn)品目錄頁面: | 601 (CN2011-ZH PDF) |

| 其它名稱: | 122-1463 |

XC18V00 Series In-System-Programmable Configuration PROMs

DS026 (v5.2) January 11, 2008

Product Specification

23

R

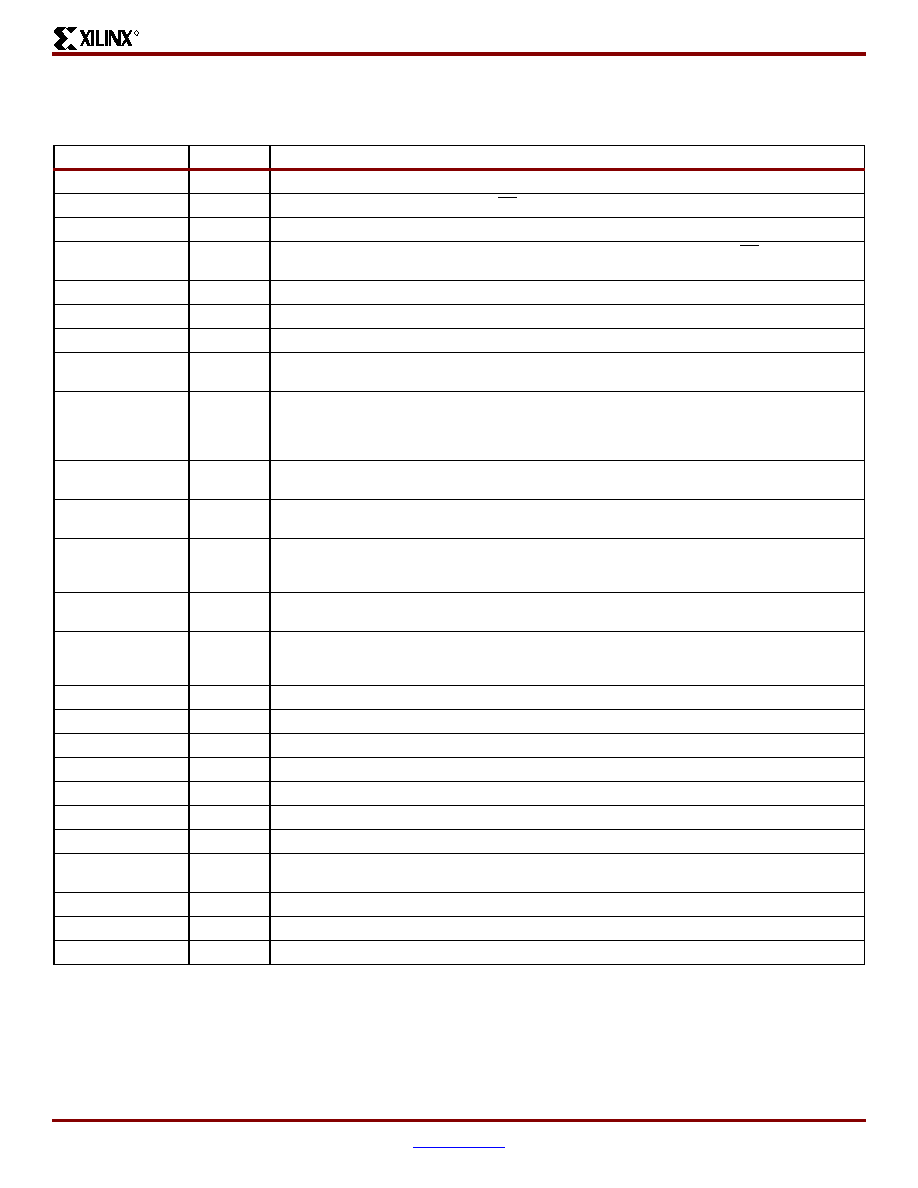

Revision History

The following table shows the revision history for this document.

Date

Version

Revision

02/09/99

1.0

First publication of this early access specification

08/23/99

1.1

Edited text, changed marking, added CF and parallel load

09/01/99

1.2

Corrected JTAG order, Security and Endurance data.

09/16/99

1.3

Corrected SelectMAP diagram, control inputs, reset polarity. Added JTAG and CF description,

256 Kbit and 128 Kbit devices.

01/20/00

2.0

Added Q44 Package, changed XC18xx to XC18Vxx

02/18/00

2.1

Updated JTAG configuration, AC and DC characteristics

04/04/00

2.2

Removed stand alone resistor on INIT pin in Figure 5. Added Virtex-E and EM parts to FPGA table.

06/29/00

2.3

Removed XC18V128 and updated format. Added AC characteristics for XC18V01, XC18V512, and

XC18V256 densities.

11/13/00

2.4

Features: changed 264 MHz to 264 Mb/s at 33 MHz; AC Spec.: TSCE units to ns, THCE CE High time

units to

μs. Removed Standby mode statement: “The lower power standby modes available on some

XC18V00 devices are set by the user in the programming software”. Changed 10,000 cycles

endurance to 20,000 cycles.

01/15/01

2.5

Updated Figures 5 and 6, added 4.7 resistors. Identification registers: changes ISP PROM product

ID from 06h to 26h.

04/04/01

2.6

Updated Figure 8, Virtex SelectMAP mode; added XC2V products to Compatible PROM table;

changed Endurance from 10,000 cycles, 10 years to 20,000, 20 years;

04/30/01

2.7

to 25 ns.

06/11/01

2.8

"AC Characteristics Over Operating Conditions for XC18V01 and XC18V512". Changed Min values

for TSCE from 20 ms to 20 ns and for THCE from 2 ms to 2 μs.

09/28/01

2.9

Changed the Boundary-Scan order for the CEO pin in Table 1, updated the configuration bits values

in the table under "Xilinx FPGAs and Compatible PROMs", and added information to the

11/12/01

3.0

Updated for Spartan-IIE FPGA family.

12/06/01

3.1

Changed Figure 5(c).

02/27/02

3.2

03/15/02

3.3

03/27/02

3.4

Made changes to pages 1-3, 5, 7-11, 13, 14, and 18. Added new Figure 9 and Figure 9.

06/14/02

3.5

Made additions and changes to Table 2.

07/24/02

3.6

Changed last bullet under Connecting Configuration PROMs, page 9.

09/06/02

3.7

Multiple minor changes throughout, plus the addition of Pinout Diagrams, page 4 and the deletion

of Figure 9.

10/31/02

3.8

Made minor change on Figure 5 (b) and changed orientation of SO20 diagram on page 5.

11/18/02

3.9

Added XC2S400E and XC2S600E to Table 2.

04/17/03

3.10

相關PDF資料 |

PDF描述 |

|---|---|

| VI-23Z-CV | CONVERTER MOD DC/DC 2V 60W |

| XC18V01SOG20C | IC PROM SERIAL CONFIG 1M 20-SOIC |

| VI-BNH-EU-B1 | CONVERTER MOD DC/DC 52V 200W |

| XCF16PVOG48C | IC PROM SRL 1.8V 16M GATE 48TSOP |

| GRM1885C1H911JA01D | CAP CER 910PF 50V 5% NP0 0603 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC18V01PCG20C0100 | 制造商:Xilinx 功能描述: |

| XC18V01PCG20C0936 | 制造商:Xilinx 功能描述:XLXXC18V01PCG20C0936 IC SYSTEM GATE |

| XC18V01PCG20C4118 | 制造商:Xilinx 功能描述: |

| XC18V01S020I | 制造商:Xilinx 功能描述: |

| XC18V01SO20 | 制造商:XILINX 制造商全稱:XILINX 功能描述:In-System Programmable Configuration PROMs |

發(fā)布緊急采購,3分鐘左右您將得到回復。