- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371311 > XC2S400E-7FG456C FPGA PDF資料下載

參數(shù)資料

| 型號: | XC2S400E-7FG456C |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁數(shù): | 10/21頁 |

| 文件大小: | 183K |

| 代理商: | XC2S400E-7FG456C |

Spartan-IIE 1.8V FPGA Family: DC and Switching Characteristics

10

www.xilinx.com

1-800-255-7778

DS077-3 (v2.0) November 18, 2002

Product Specification

R

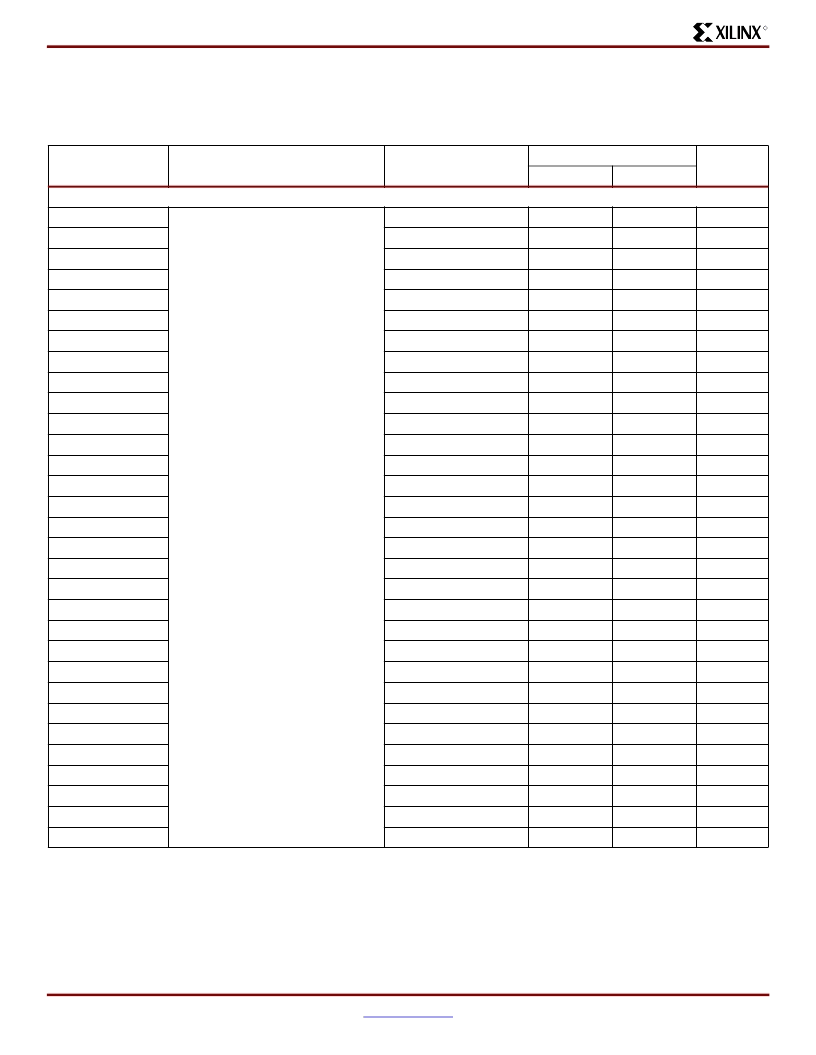

IOB Output Delay Adjustments for Different Standards(1)

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust

the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

Symbol

Description

Standard

Speed Grade

-7

Units

-6

Output Delay Adjustments (Adj)

T

OLVTTL_S2

T

OLVTTL_S4

T

OLVTTL_S6

T

OLVTTL_S8

T

OLVTTL_S12

T

OLVTTL_S16

T

OLVTTL_S24

T

OLVTTL_F2

T

OLVTTL_F4

T

OLVTTL_F6

T

OLVTTL_F8

T

OLVTTL_F12

T

OLVTTL_F16

T

OLVTTL_F24

T

OLVCMOS2

T

OLVCMOS18

T

OLVDS

T

OLVPECL

T

OPCI33_3

T

OPCI66_3

T

OGTL

T

OGTLP

T

OHSTL_I

T

OHSTL_III

T

OHSTL_IV

T

OSSTL2_I

T

OSSLT2_II

T

OSSTL3_I

T

OSSTL3_II

T

OCTT

T

OAGP

Notes:

1.

Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. For other I/O standards and different loads, see the

tables

Constants for Calculating T

IOOP

and

Delay Measurement Methodology

, page 11

.

Standard-specific adjustments for

output delays terminating at pads

(based on standard capacitive

load, C

SL

)

LVTTL, Slow, 2 mA

14.7

7.5

4.8

3.0

1.9

1.7

1.3

13.1

5.3

3.1

1.0

0

–

0.05

–

0.20

0.09

0.7

–

1.2

–

0.41

2.3

–

0.41

0.49

0.8

–

0.51

–

0.91

–

1.01

–

0.51

–

0.91

–

0.51

–

1.01

–

0.61

–

0.91

14.7

7.5

4.8

3.0

1.9

1.7

1.3

13.1

5.3

3.1

1.0

0

–

0.05

–

0.20

0.09

0.7

–

1.2

–

0.41

2.3

–

0.41

0.49

0.8

–

0.51

–

0.91

–

1.01

–

0.51

–

0.91

–

0.51

–

1.01

–

0.61

–

0.91

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

4 mA

6 mA

8 mA

12 mA

16 mA

24 mA

LVTTL, Fast, 2 mA

4 mA

6 mA

8 mA

12 mA

16 mA

24 mA

LVCMOS2

LVCMOS18

LVDS

LVPECL

PCI, 33 MHz, 3.3V

PCI, 66 MHz, 3.3V

GTL

GTL+

HSTL I

HSTL III

HSTL IV

SSTL2 I

SSTL2 II

SSTL3 I

SSTL3 II

CTT

AGP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2S400E-7FG676C | FPGA |

| XC2S400E-7FT256C | FPGA |

| XC2S600E-6FG456C | FPGA |

| XC2S600E-6FG456I | FPGA |

| XC2S600E-6FG676C | FPGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S400E-7FG456I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FG676C | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 400K GATES 10800 CELLS 400MHZ 1.8V 676FBGA - Trays |

| XC2S400E-7FG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG456C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S400E-7FGG456I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。