- 您現(xiàn)在的位置:買賣IC網 > PDF目錄21989 > XC2S50-5PQG208C (Xilinx Inc)IC SPARTAN-II FPGA 50K 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC2S50-5PQG208C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 26/99頁 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-II FPGA 50K 208-PQFP |

| 標準包裝: | 24 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 384 |

| 邏輯元件/單元數(shù): | 1728 |

| RAM 位總計: | 32768 |

| 輸入/輸出數(shù): | 140 |

| 門數(shù): | 50000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應商設備封裝: | 208-PQFP(28x28) |

| 產品目錄頁面: | 599 (CN2011-ZH PDF) |

| 其它名稱: | 122-1320 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

32

R

Using Block RAM Features

The Spartan-II FPGA family provides dedicated blocks of

on-chip, true dual-read/write port synchronous RAM, with

4096 memory cells. Each port of the block RAM memory

can be independently configured as a read/write port, a

read port, a write port, and can be configured to a specific

data width. The block RAM memory offers new capabilities

allowing the FPGA designer to simplify designs.

Operating Modes

Block RAM memory supports two operating modes.

Read Through

Write Back

Read Through (One Clock Edge)

The read address is registered on the read port clock edge

and data appears on the output after the RAM access time.

Some memories may place the latch/register at the outputs

depending on the desire to have a faster clock-to-out versus

setup time. This is generally considered to be an inferior

solution since it changes the read operation to an

asynchronous function with the possibility of missing an

address/control line transition during the generation of the

read pulse clock.

Write Back (One Clock Edge)

The write address is registered on the write port clock edge

and the data input is written to the memory and mirrored on

the write port input.

Block RAM Characteristics

1.

All inputs are registered with the port clock and have a

setup to clock timing specification.

2.

All outputs have a read through or write back function

depending on the state of the port WE pin. The outputs

relative to the port clock are available after the

clock-to-out timing specification.

3.

The block RAM are true SRAM memories and do not

have a combinatorial path from the address to the

output. The LUT cells in the CLBs are still available with

this function.

4.

The ports are completely independent from each other

(i.e., clocking, control, address, read/write function, and

data width) without arbitration.

5.

A write operation requires only one clock edge.

6.

A read operation requires only one clock edge.

The output ports are latched with a self timed circuit to

guarantee a glitch free read. The state of the output port will

not change until the port executes another read or write

operation.

Library Primitives

RAM primitives. Table 11 describes all of the available

primitives for synthesis and simulation.

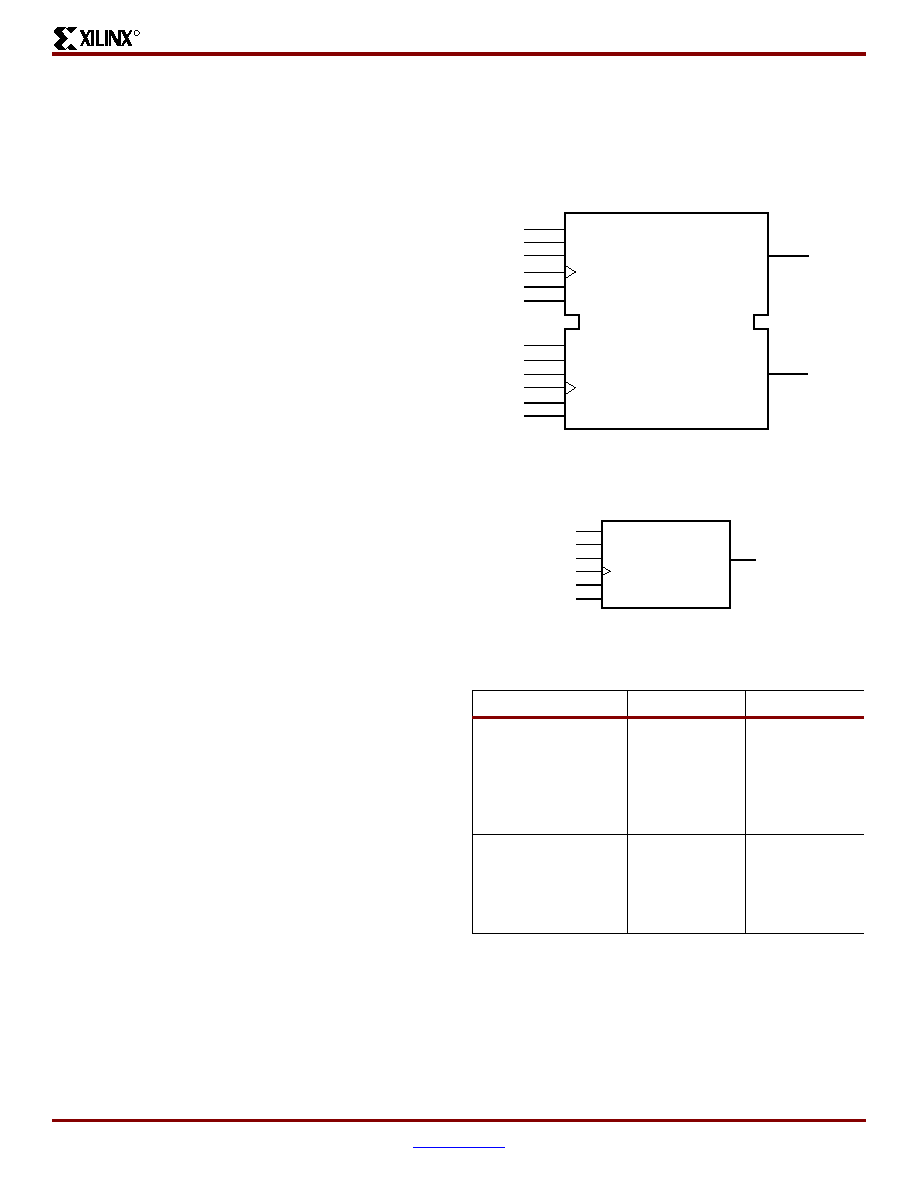

Figure 31: Dual-Port Block RAM Memory

Figure 32: Single-Port Block RAM Memory

Table 11: Available Library Primitives

Primitive

Port A Width

Port B Width

RAMB4_S1

RAMB4_S1_S1

RAMB4_S1_S2

RAMB4_S1_S4

RAMB4_S1_S8

RAMB4_S1_S16

1

2

4

8

16

RAMB4_S2

RAMB4_S2_S2

RAMB4_S2_S4

RAMB4_S2_S8

RAMB4_S2_S16

2N/A

2

4

8

16

WEB

ENB

RSTB

CLKB

ADDRB[#:0]

DIB[#:0]

WEA

ENA

RSTA

CLKA

ADDRA[#:0]

DIA[#:0]

DOA[#:0]

DOB[#:0]

RAMB4_S#_S#

DS001_31_061200

DS001_32_061200

DO[#:0]

WE

EN

RST

CLK

ADDR[#:0]

DI[#:0]

RAMB4_S#

相關PDF資料 |

PDF描述 |

|---|---|

| FMC13DRYN-S734 | CONN EDGECARD 26POS DIP .100 SLD |

| TACR336M010RTA | CAP TANT 33UF 10V 20% 0805 |

| XC3S250E-4VQG100C | IC SPARTAN-3E FPGA 250K 100VQFP |

| FMC13DRYH-S734 | CONN EDGECARD 26POS DIP .100 SLD |

| XC3S100E-4TQG144I | IC FPGA SPARTAN-3E 100K 144-TQFP |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S50-5PQG208I | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 50K GATES 1728 CELLS 263MHZ 2.5V 208PQFP - Trays |

| XC2S50-5TQ144C | 功能描述:IC FPGA 2.5V 384 CLB'S 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應商設備封裝:676-FBGA(27x27) |

| XC2S50-5TQ144C-ES | 制造商:Xilinx 功能描述:2S50-5TQ144C-ES |

| XC2S50-5TQ144I | 功能描述:IC FPGA 2.5V I-TEMP 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應商設備封裝:676-FBGA(27x27) |

| XC2S50-5TQG144C | 功能描述:IC SPARTAN-II FPGA 50K 144-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-II 標準包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計:221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應商設備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

發(fā)布緊急采購,3分鐘左右您將得到回復。