- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4131 > XC3090A-7TQ176C (Xilinx Inc)IC LOGIC GATE ARRAY, 176TQFP PDF資料下載

參數(shù)資料

| 型號: | XC3090A-7TQ176C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 7/76頁 |

| 文件大小: | 0K |

| 描述: | IC LOGIC GATE ARRAY, 176TQFP |

| 標準包裝: | 40 |

| 系列: | XC3000A/L |

| LAB/CLB數(shù): | 320 |

| RAM 位總計: | 64160 |

| 輸入/輸出數(shù): | 144 |

| 門數(shù): | 6000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 176-LQFP |

| 供應商設(shè)備封裝: | 176-TQFP(24x24) |

| 其它名稱: | Q1151314 XC3090A7TQ176C |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

R

November 9, 1998 (Version 3.1)

7-17

XC3000 Series Field Programmable Gate Arrays

7

A buffer in the upper left corner of the FPGA chip drives a

global net which is available to all K inputs of logic blocks.

Using the global buffer for a clock signal provides a

skew-free, high fan-out, synchronized clock for use at any

or all of the IOBs and CLBs. Configuration bits for the K

input to each logic block can select this global line or

another routing resource as the clock source for its

flip-flops. This net may also be programmed to drive the die

edge clock lines for IOB use. An enhanced speed, CMOS

threshold, direct access to this buffer is available at the sec-

ond pad from the top of the left die edge.

A buffer in the lower right corner of the array drives a hori-

zontal Longline that can drive programmed connections to

a vertical Longline in each interconnection column. This

alternate buffer also has low skew and high fan-out. The

network formed by this alternate buffer’s Longlines can be

selected to drive the K inputs of the CLBs. CMOS thresh-

old, high speed access to this buffer is available from the

third pad from the bottom of the right die edge.

Internal Busses

A pair of 3-state buffers, located adjacent to each CLB, per-

mits logic to drive the horizontal Longlines. Logic operation

of the 3-state buffer controls allows them to implement wide

multiplexing functions. Any 3-state buffer input can be

selected as drive for the horizontal long-line bus by apply-

ing a Low logic level on its 3-state control line. See

Figure 16. The user is required to avoid contention which

can result from multiple drivers with opposing logic levels.

Control of the 3-state input by the same signal that drives

the buffer input, creates an open-drain wired-AND function.

A logic High on both buffer inputs creates a high imped-

ance, which represents no contention. A logic Low enables

the buffer to drive the Longline Low. See Figure 17. Pull-up

resistors are available at each end of the Longline to pro-

vide a High output when all connected buffers are non-con-

ducting. This forms fast, wide gating functions. When data

drives the inputs, and separate signals drive the 3-state

control lines, these buffers form multiplexers (3-state bus-

ses). In this case, care must be used to prevent contention

through multiple active buffers of conflicting levels on a

common line. Each horizontal Longline is also driven by a

weak keeper circuit that prevents undefined floating levels

by maintaining the previous logic level when the line is not

driven by an active buffer or a pull-up resistor. Figure 18

shows 3-state buffers, Longlines and pull-up resistors.

3-STATE CONTROL

GG

HG

P40

P41

P42

P43

RST

P46

.l

X1245

.q

.Q

OS

C

P47

BCL

KIN

P48

GH

HH

.lk

.ck

I/O CLOCKS

BIDIRECTIONAL

INTERCONNECT

BUFFERS

GLOBAL NET

3 VERTICAL LONG

LINES PER COLUMN

HORIZONTAL LONG LINE

PULL-UP RESISTOR

HORIZONTAL LONG LINE

OSCILLATOR

AMPLIFIER OUTPUT

DIRECTINPUT OF P47

TO AUXILIARY BUFFER

CRYSTAL OSCILLATOR

BUFFER

3-STATE INPUT

3-STATE BUFFER

ALTERNATE BUFFER

D

P

G

M

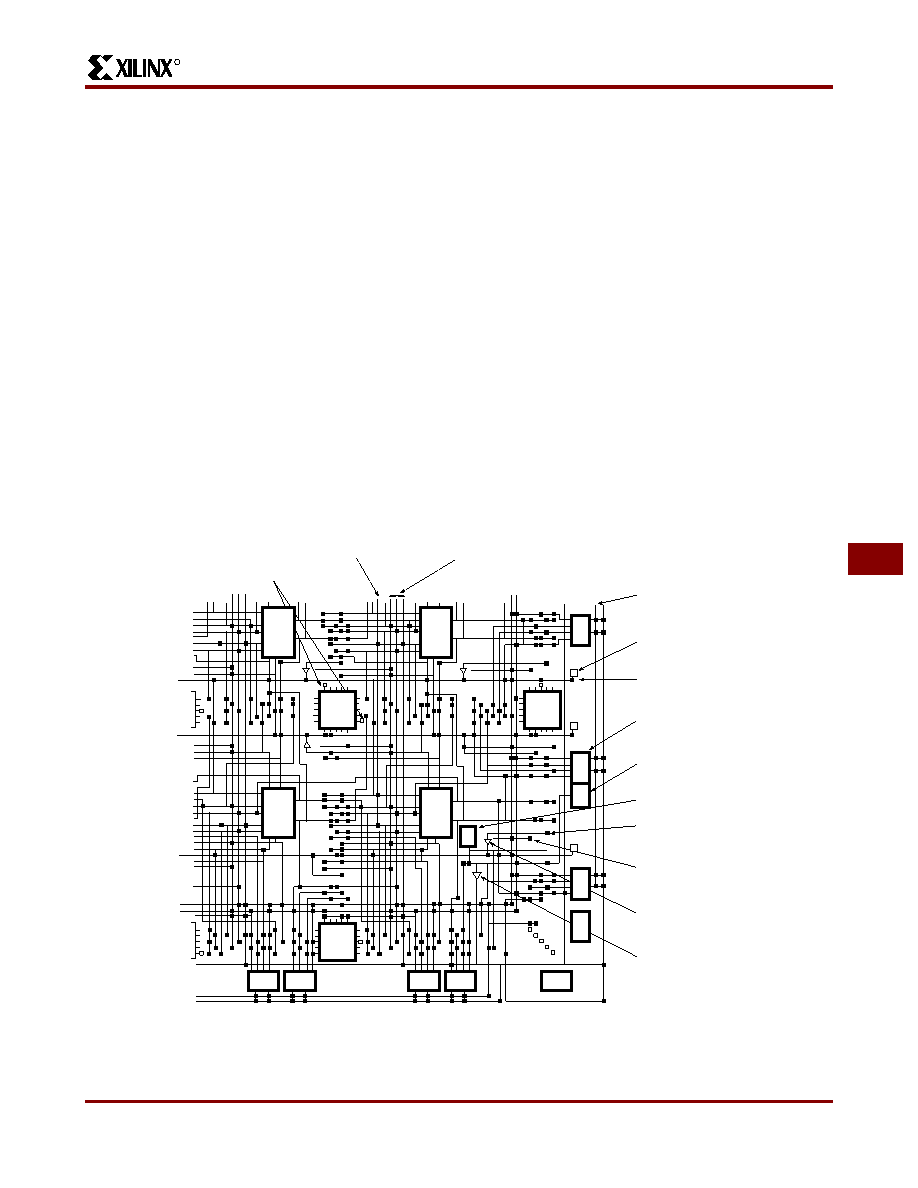

Figure 18: Design Editor.

An extra large view of possible interconnections in the lower right corner of the XC3020A.

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5VLX50T-1FFG665CES | IC FPGA VIRTEX-5 ES 50K 665FCBGA |

| AMM31DTAT-S189 | CONN EDGECARD 62POS R/A .156 SLD |

| ACC60DRAN | CONN EDGECARD 120PS .100 R/A DIP |

| ACC60DRAH | CONN EDGECARD 120PS .100 R/A DIP |

| ACB65DHBT | CONN EDGECARD 130PS R/A .050 DIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3090A-7TQ176I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3090B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| XC3090L | 制造商:XILINX 制造商全稱:XILINX 功能描述:Logic Cell Array Families |

| XC3090L-8PC84C | 功能描述:IC FPGA 3.3V C-TEMP 84-PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:XC3000A/L 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XC3090L-8PC84I | 功能描述:IC FPGA 3.3V I-TEMP 84-PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:XC3000A/L 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應商設(shè)備封裝:120-CPGA(34.55x34.55) |

發(fā)布緊急采購,3分鐘左右您將得到回復。