- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4176 > XC3164A-3PC84C (Xilinx Inc)IC LOGIC CL ARRAY 6400GAT 84PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | XC3164A-3PC84C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 75/76頁(yè) |

| 文件大小: | 0K |

| 描述: | IC LOGIC CL ARRAY 6400GAT 84PLCC |

| 產(chǎn)品變化通告: | XC4000XL/E, XC9500XV, XC3100A Discontinuance 12/Apr/2010 |

| 標(biāo)準(zhǔn)包裝: | 15 |

| 系列: | XC3000A/L |

| LAB/CLB數(shù): | 224 |

| RAM 位總計(jì): | 46064 |

| 輸入/輸出數(shù): | 70 |

| 門數(shù): | 4500 |

| 電源電壓: | 4.25 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 84-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 84-PLCC |

| 其它名稱: | 122-1045 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)當(dāng)前第75頁(yè)第76頁(yè)

R

XC3000 Series Field Programmable Gate Arrays

7-10

November 9, 1998 (Version 3.1)

Flexible routing allows use of common or individual CLB

clocking.

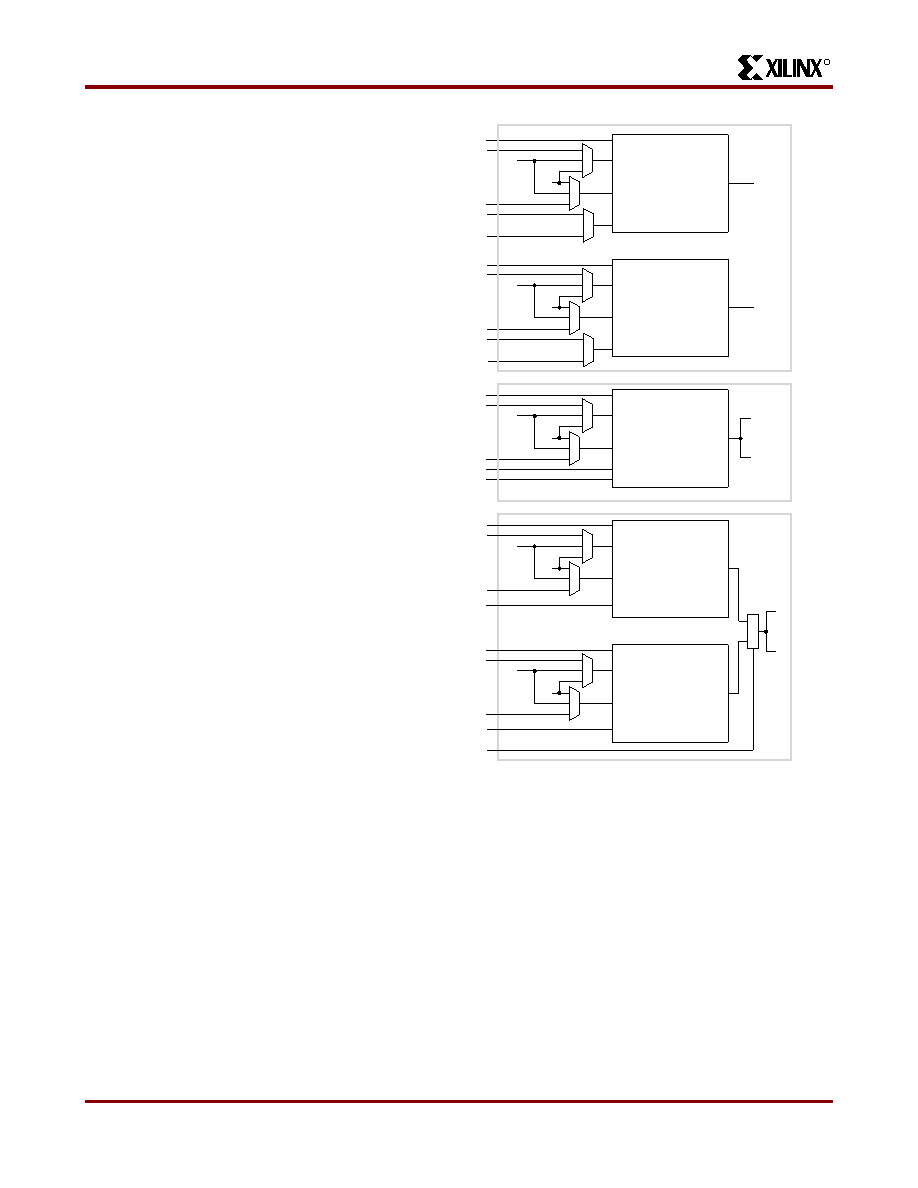

The combinatorial-logic portion of the CLB uses a 32 by 1

look-up table to implement Boolean functions. Variables

selected from the five logic inputs and two internal block

flip-flops are used as table address inputs. The combinato-

rial propagation delay through the network is independent

of the logic function generated and is spike free for single

input variable changes. This technique can generate two

independent logic functions of up to four variables each as

shown in Figure 6a, or a single function of five variables as

shown in Figure 6b, or some functions of seven variables

as shown in Figure 6c. Figure 7 shows a modulo-8 binary

counter with parallel enable. It uses one CLB of each type.

The partial functions of six or seven variables are imple-

mented using the input variable (E) to dynamically select

between two functions of four different variables. For the

two functions of four variables each, the independent

results (F and G) may be used as data inputs to either

flip-flop or either logic block output. For the single function

of five variables and merged functions of six or seven vari-

ables, the F and G outputs are identical. Symmetry of the F

and G functions and the flip-flops allows the interchange of

CLB outputs to optimize routing efficiencies of the networks

interconnecting the CLBs and IOBs.

Programmable Interconnect

Programmable-interconnection resources in the Field Pro-

grammable Gate Array provide routing paths to connect

inputs and outputs of the IOBs and CLBs into logic net-

works. Interconnections between blocks are composed of a

two-layer grid of metal segments. Specially designed pass

transistors, each controlled by a configuration bit, form pro-

grammable interconnect points (PIPs) and switching matri-

ces used to implement the necessary connections between

selected metal segments and block pins. Figure 8 is an

example of a routed net. The development system provides

automatic routing of these interconnections. Interactive

routing is also available for design optimization. The inputs

of the CLBs or IOBs are multiplexers which can be pro-

grammed to select an input network from the adjacent

interconnect segments.

Since the switch connections to

block inputs are unidirectional, as are block outputs,

they are usable only for block input connection and not

for routing. Figure 9 illustrates routing access to logic

block input variables, control inputs and block outputs.

Three types of metal resources are provided to accommo-

date various network interconnect requirements.

General Purpose Interconnect

Direct Connection

Longlines (multiplexed busses and wide AND gates)

QY

Any Function

of Up to 4

Variables

QY

Any Function

of Up to 4

Variables

QY

Any Function

of 5 Variables

QY

Any Function

of Up to 4

Variables

QY

Any Function

of Up to 4

Variables

5c

5b

5a

QX

A

B

C

D

A

B

C

D

E

A

B

C

D

E

D

A

B

C

D

C

A

B

M

U

X

F

G

F

G

F

G

E

X5442

FGM

Mode

Figure 6: Combinational Logic Options

6a. Combinatorial Logic Option FG generates two func-

tions of four variables each. One variable, A, must be

common to both functions. The second and third variable

can be any choice of B, C, QX and QY. The fourth vari-

able can be any choice of D or E.

6b. Combinatorial Logic Option F generates any function

of five variables: A, D, E and two choices out of B, C, QX,

QY.

6c. Combinatorial Logic Option FGM allows variable E to

select between two functions of four variables: Both have

common inputs A and D and any choice out of B, C, QX

and QY for the remaining two variables. Option 3 can

then implement some functions of six or seven variables.

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AMC36DRYN-S13 | CONN EDGECARD 72POS .100 EXTEND |

| XC3142A-3PQ100C | IC LOGIC CL ARRAY 4200GAT 100PQF |

| AMC36DRYH-S13 | CONN EDGECARD 72POS .100 EXTEND |

| XC3130A-3PQ100C | IC LOGIC CL ARRAY 3000GAT 100PQF |

| XC3130A-3PC84C | IC LOGIC CL ARRAY 3000GAT 84PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3164A-3PC84I | 制造商:Xilinx 功能描述: |

| XC3164A-3PQ160C | 制造商:Xilinx 功能描述: |

| XC3164A-3PQ160I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3164A-3TQ144C | 功能描述:IC FPGA 224 CLB'S 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:XC3000A/L 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XC3164A-3TQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。