- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300144 > XC4000XLASERIES (Xilinx, Inc.) Field Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號(hào): | XC4000XLASERIES |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Field Programmable Gate Arrays |

| 中文描述: | 現(xiàn)場(chǎng)可編程門(mén)陣列 |

| 文件頁(yè)數(shù): | 12/14頁(yè) |

| 文件大小: | 142K |

| 代理商: | XC4000XLASERIES |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)

R

DS015 (v1.3) October 18, 1999 - Product Specication

6-163

XC4000XLA/XV Field Programmable Gate Arrays

6

I/O Signalling Standards

XLA and XV devices are compatible with TTL, LVTTL, PCI

3V, PCI 5V and LVCMOS signalling. The various standards

are illustrated in Table 6 and the signaling environment is

illustrated in Figure 4.

VCC Clamping

XLA/XV devices are fully 5V TTL I/O compatible if VCC

clamping is not enabled. The I/O pins can withstand input

voltages up to 7V. With VCC clamping enabled, the XLA/XV

devices will begin to clamp input voltages to one diode volt-

age drop above VCC. In both cases negative voltage is

clamped to one diode voltage drop below ground.

XLA/XV devices maintain LVTTL I/O compatibility when

VCC clamping is enabled, however full 5.0V TTL I/O com-

patibility is sacriced.

Overshoot and Undershoot

Ringing wave forms are allowed on XLA/XV inputs as long

as undershoot is limited to -2.0V and overshoot is limited to

+7.0V and current is limited to 100 mA for less than 10 ns.

If VCC clamping is enabled then overshoot will begin to be

clamped at VCC/VCCIO plus one diode voltage drop and

undershoot will be clamped to ground minus one diode volt-

age drop. In either case the current must be limited to 100

mA per pin for less than 10 ns.

Express Conguration Mode

Express conguration mode is similar to Slave Serial con-

guration mode, except that data is processed one byte per

CCLK cycle instead of one bit per CCLK cycle. An external

source is used to drive CCLK, while byte-wide data is

loaded directly into the conguration data shift registers

(Figure 5). A CCLK frequency of 10 MHz is equivalent to a

80 MHz serial rate, because eight bits of conguration data

are loaded per CCLK cycle. Express mode does not sup-

port CRC error checking, but does support constant-eld

error checking. A length count is not used in Express mode.

Express mode must be specied as an option to the BitGen

program, which generates the bitstream. The Express

mode bitstream is not compatible with the other congura-

tion modes. Express mode is selected by a <010> on the

mode pins (M2, M1, M0).

The rst byte of parallel conguration data must be avail-

able at the D inputs of the FPGA a short setup time before

the second rising CCLK edge. Subsequent data bytes are

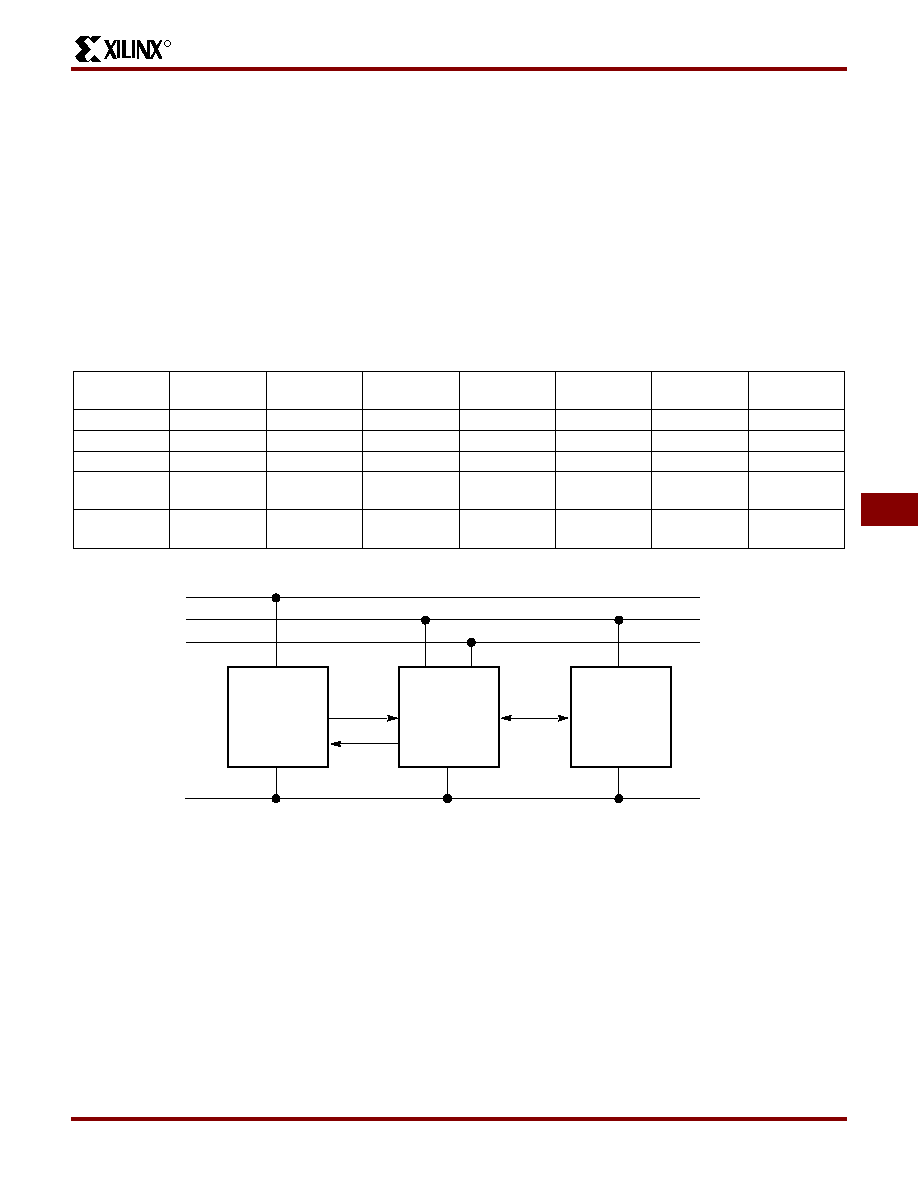

Table 6: I/O Standards supported by XC4000XLA and XV FPGAs

Signaling

Standard

VCC

Clamping

Output Drive

VIH_MAX

VIH MIN

VIL MAX

VOH MIN

VOL MAX

TTL

Not allowed

12/24 mA

5.5

2.0

0.8

2.4

0.4

LVTTL

OK

12/24 mA

3.6

2.0

0.8

2.4

0.4

PCI5V

Not allowed

24 mA

5.5

2.0

0.8

2.4

0.4

PCI3V

Required

12 mA

3.6

50% of

VCC/VCCIO

30% of

VCC/VCCIO

90% of

VCC/VCCIO

10% of

VCC/VCCIO

LVCMOS 3V

OK

12/24 mA

3.6

50% of

VCC/VCCIO

30% of

VCC/VCCIO

90% of

VCC/VCCIO

10% of

VCC/VCCIO

VCC (5 V)

5.0 V Power

3.3 V Power

2.5 V Power

Ground

TTL

LVTTL

5 Volt Device

VCCIO VCCINT

LVTTL

XC4000XV

VCC (3.3 V)

3.3 Volt Device

X7147

Figure 4: The Signalling Environment for XLA/XV FPGAS. For XLA devices the VCCIO and VCCINT supplies are

replaced by a single 3.3 Volt VCC supply, however, all indicated I/O signalling is still supported.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC4013E-1CB240M | Programmable Gate Arrays |

| XC4013E-1HG240C | Programmable Gate Arrays |

| XC4013E-3BG240M | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-1VQ240M | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-2BG240C | XC4000E and XC4000X Series Field Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC4000XSERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Programmable Gate Arrays |

| XC4000XV | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC4000XLA/XV Field Programmable Gate Arrays |

| XC4000XVSERIES | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC4002 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| XC4002A | 制造商:XILINX 制造商全稱:XILINX 功能描述:Logic Cell Array Families |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。