- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4239 > XC4VFX12-12SFG363C (Xilinx Inc)IC FPGA VIRTEX-4 FX 12K 363FCBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC4VFX12-12SFG363C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 26/58頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA VIRTEX-4 FX 12K 363FCBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Virtex®-4 FX |

| LAB/CLB數(shù): | 1368 |

| 邏輯元件/單元數(shù): | 12312 |

| RAM 位總計(jì): | 663552 |

| 輸入/輸出數(shù): | 240 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 363-FBGA,F(xiàn)CBGA |

| 供應(yīng)商設(shè)備封裝: | 363-FCBGA(17x17) |

| 配用: | HW-V4-ML403-UNI-G-ND - EVALUATION PLATFORM VIRTEX-4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

Virtex-4 FPGA Data Sheet: DC and Switching Characteristics

DS302 (v3.7) September 9, 2009

Product Specification

32

CLB Distributed RAM Switching Characteristics (SLICEM Only)

)

CLB Shift Register Switching Characteristics (SLICEM Only)

)

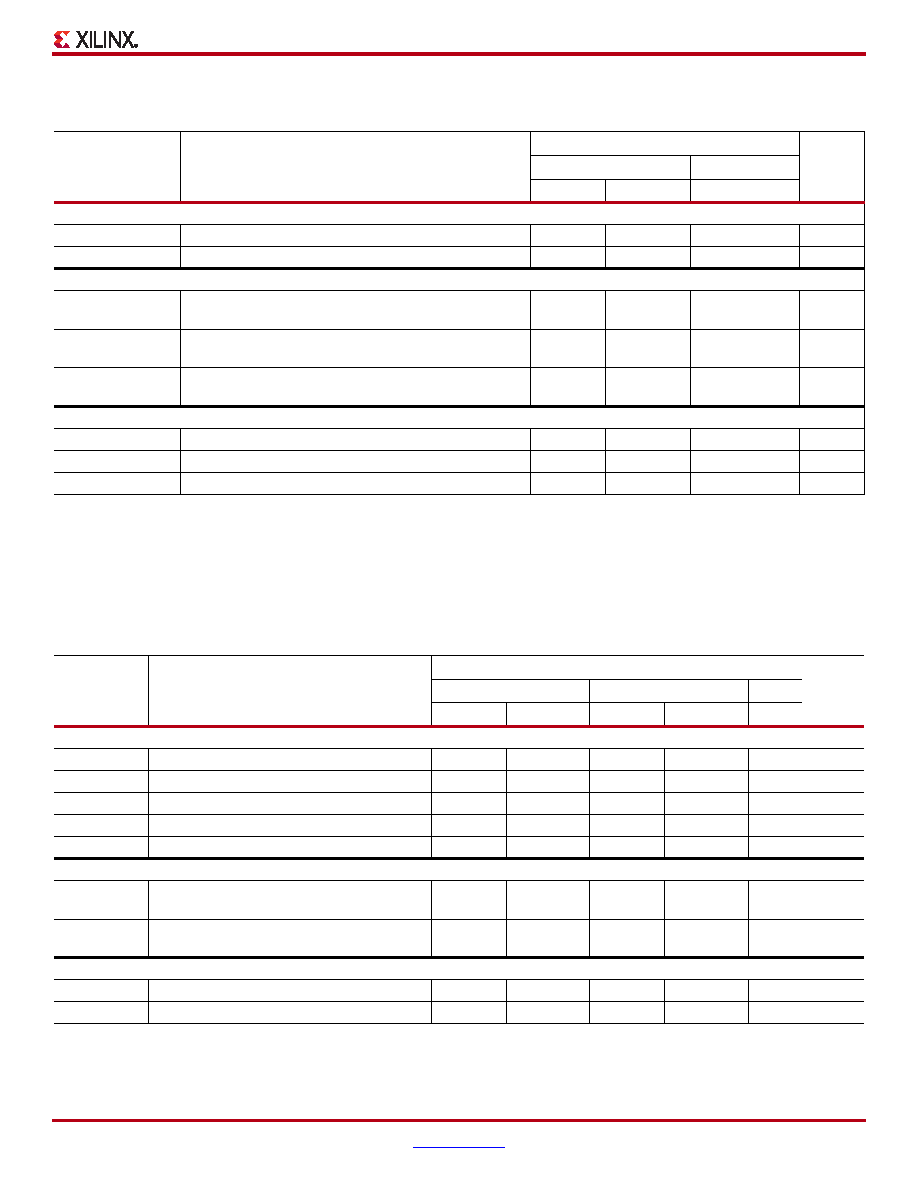

Table 38: CLB Distributed RAM Switching Characteristics

Symbol

Description

Speed Grade

Units

-12

-11

-10

XC4VFX(2)

XC4VLX/SX

ALL DEVICES

Sequential Delays

TSHCKO

Clock CLK to X outputs (WE active)(3)

1.61

1.58

1.77

2.08

ns, Max

TSHCKOF5

Clock CLK to F5 output (WE active)

1.53

1.50

1.69

1.98

ns, Max

Setup and Hold Times Before/After Clock CLK

TDS / TDH

BX/BY data inputs (DI)

1.26

–0.90

1.23

–0.88

1.46

–0.88

1.80

–0.88

ns, Min

TAS / TAH

F/G address inputs

0.88

–0.37

0.86

–0.37

0.97

–0.34

1.13

–0.29

ns, Min

TWS / TWH

WE input (SR)

1.10

–0.48

1.08

–0.47

1.21

–0.47

1.42

–0.47

ns, Min

Clock CLK

TWPH

Minimum Pulse Width, High

0.53

0.52

0.59

0.69

ns, Min

TWPL

Minimum Pulse Width, Low

0.55

0.54

0.60

0.70

ns, Min

TWC

Minimum clock period to meet address write cycle time

0.76

0.74

0.84

0.98

ns, Min

Notes:

1.

A Zero “0” Hold Time listing indicates no hold time or a negative hold time. Negative values cannot be guaranteed “best-case,” but if a “0” is listed,

there is no positive hold time.

2.

The values in this column apply to all XC4VFX -12 parts except XC4VFX12 -12. For XC4VFX12 -12 values, use the values in the adjacent

XC4VLX/SX -12 column.

3.

TSHCKO also represents the CLK to XMUX output. Refer to TRCE report for the CLK to XMUX path.

Table 39: CLB Shift Register Switching Characteristics

Symbol

Description

Speed Grade

Units

-12

-11

-10

XC4VFX(2)

XC4VLX/SX

XC4VFX(3)

XC4VLX/SX

ALL

Sequential Delays

TREG

Clock CLK to X/Y outputs

2.12

2.08

2.19

2.57

ns, Max

TREGXB

Clock CLK to XB output via MC15 LUT output

1.83

1.73

1.90

1.84

2.16

ns, Max

TREGYB

Clock CLK to YB output via MC15 LUT output

1.84

1.74

1.92

1.85

2.17

ns, Max

TCKSH

Clock CLK to Shiftout

1.70

1.60

1.76

1.70

1.99

ns, Max

TREGF5

Clock CLK to F5 output

2.05

2.01

2.11

2.47

ns, Max

Setup and Hold Times Before/After Clock CLK

TWS / TWH

WE input (SR)

0.87

–0.76

0.85

–0.76

0.96

–0.70

0.96

–0.70

1.12

–0.62

ns, Min

TDS / TDH

BX/BY data inputs (DI)

1.28

–1.12

1.25

–1.11

1.45

–1.11

1.45

–1.11

1.75

–1.11

ns, Min

Clock CLK

TWPH

Minimum Pulse Width, High

0.53

0.52

0.59

0.69

ns, Min

TWPL

Minimum Pulse Width, Low

0.55

0.54

0.60

0.70

ns, Min

Notes:

1.

A Zero “0” Hold Time listing indicates no hold time or a negative hold time. Negative values cannot be guaranteed “best-case,” but if a “0” is listed,

there is no positive hold time.

2.

The values in this column apply to all XC4VFX -12 parts except XC4VFX12 -12. For XC4VFX12 -12 values, use the values in the adjacent

XC4VLX/SX -12 column.

3.

The values in this column apply to all XC4VFX -11 parts.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC4VFX12-11SFG363I | IC FPGA VIRTEX-4 FX 12K 363FCBGA |

| HMC60DREN-S13 | CONN EDGECARD 120PS .100 EXTEND |

| HMC60DREH-S13 | CONN EDGECARD 120PS .100 EXTEND |

| ACC50DRST-S273 | CONN EDGECARD 100PS DIP .100 SLD |

| XC6SLX150T-N3FGG676C | IC FPGA SPARTAN-6 676FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC4VFX140 | 制造商:XILINX 制造商全稱:XILINX 功能描述:DC and Switching Characteristics |

| XC4VFX140-10FF1152C | 制造商:Xilinx 功能描述: |

| XC4VFX140-10FF1517C | 制造商:Xilinx 功能描述:FPGA VIRTEX-4 142128 CELLS 90NM 1.2V 1517FCBGA - Trays |

| XC4VFX140-10FF1517CES4 | 制造商:Xilinx 功能描述: |

| XC4VFX140-10FF1517I | 功能描述:IC FPGA VIRTEX-4FX 1517FFBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Virtex®-4 FX 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。